Kazalo vsebine

- Izvršni povzetek: 2025 in pot naprej

- Tržni delež in napovedi rasti do leta 2030

- Ključni dejavniki: AI, IoT in napredno proizvodnjo vozlišč

- Ultrapure standardi: Spreminjajoče se zahteve in industrijski standardi

- Najnovejše inovacije v metodologijah testiranja redundance

- Glavni akterji in strateška zavezništva (osredotočenost na 2025)

- Integracija dobavne verige in izzivi čistoče

- Regulativno okolje in standardne organizacije (npr. SEMI.org, IEEE.org)

- Novi trgi in regionalne priložnosti

- Strateški pregled: Motilne tehnologije in dolgoročni trendi

- Viri in reference

Izvršni povzetek: 2025 in pot naprej

Testiranje redundance v ultrapure polprevodniških procesih pridobiva ključno moč, ko industrija vstopa v leto 2025, kar je posledica neomajnega pritiska za manjša vozlišča, večjo zanesljivost naprav in proliferacijo naprednih aplikacij, kot so AI, avtomobilska elektronika in kvantno računanje. Ultrapure okolja so ključnega pomena za dosego strogih zahtev po donosu in zanesljivosti pri proizvodnji čipov pod 5nm in naslednje generacije. Testiranje redundance – kjer se sistematično preverjajo rezervni krogi in arhitekture odporne na napake – je postalo ključnega pomena za zagotavljanje odpornosti proizvodnje, zmanjšanje dragih izpadov in obravnavo latentnih napak, ki lahko izhajajo tudi iz najmanjših nečistoč ali procesnih variacij.

Vodili proizvajalci polprevodnikov večajo naložbe v testiranje redundance znotraj ultrapure okolij. Na primer, podjetje Taiwan Semiconductor Manufacturing Company (TSMC) še naprej povečuje svoj fokus na validacijo redundance kot del svojih strategij za napredno obvladovanje procesov in upravljanje napak, zlasti pri svojih 3nm in 2nm vozliščih. Podobno je podjetje Samsung Electronics Semiconductor poudarilo integracijo mehanizmov redundance in sofisticiranih testnih protokolov v svojih najsodobnejših tovarnah, s ciljem dodatno okrepiti zanesljivost naprav, ko prehajajo na arhitekture tranzistorjev “gate-all-around” (GAA).

Dobavitelji opreme se prav tako prilagajajo tem zahtevam. Podjetji Applied Materials in Lam Research inovirata orodja za inšpekcijo waferjev in metrologijo, ki izkoriščajo analitiko, ki jo poganja AI, za bolj učinkovito odkrivanje in karakterizacijo napak redundance v ultrapure procesnih linijah. Ti sistemi se uvedejo za spremljanje procesno povzročene napakovitosti in potrjevanje operativne celovitosti redundantnih struktur.

Podatki iz industrijskih konsorcijev, kot je SEMI, kažejo, da naj bi naložbe v testiranje in metrologijo za napredne sheme redundance rasle s CAGR, ki bo presegla 7% do leta 2028, kar odraža prioritetno usmeritev sektorja k upravljanju donosa in zagotavljanju zanesljivosti. Poleg tega sodelovalna prizadevanja, kot so tista pri imec, pospešujejo razvoj novih arhitektur redundance in proizvodnih protokolov, prilagojenih za ultrapure okolja.

V prihodnjih letih bo testiranje redundance postalo vse bolj avtomatizirano, osredotočeno na podatke in tesno integrirano z nadzorom procesov v realnem času. Ker se proizvajalci polprevodnikov usmerjajo proti 2nm in naprej, bo paradigma ničelne napake odvisna od napredkov tako v oblikovanju redundance kot v testiranju znotraj ultrapure nastavitev. Ta evolucija bo ključna za ohranjanje zanesljivosti, razširljivosti in komercialne življenjske sposobnosti prihodnjih polprevodniških tehnologij.

Tržni delež in napovedi rasti do leta 2030

Globalni trg za ultrapure testiranje redundance polprevodnikov je pripravljen na pomembno rast do leta 2030, kar je posledica naraščajoče kompleksnosti naprav, proliferacije naprednih vozlišč (5nm, 3nm in manj) ter rastočega povpraševanja po ultra-zanesljivih čipih v kritičnih aplikacijah, kot so avtomobilstvo, podatkovni centri in AI. Ker se geometrije naprav zmanjšujejo in raven integracije narašča, potreba po zagotavljanju absolutne čistoče in robustnosti v procesih proizvodnje polprevodnikov postavlja testiranje redundance na čelo zagotavljanja kakovosti.

V letu 2025 vodilni proizvajalci polprevodnikov, kot so Taiwan Semiconductor Manufacturing Company (TSMC), Samsung Electronics in Intel Corporation, še naprej povečujejo svoje naložbe v infrastrukturo naprednega testiranja redundance. Te naložbe so usmerjene ne le v odkrivanje in obvladovanje latentnih napak v logičnih in pomnilniških vezjih, temveč tudi v izpolnjevanje vse strožjih zahtev po zanesljivosti, ki jih zahtevajo avtomobilski in misijsko kritični sektorji. Na primer, nadaljevanje širitev kapacitet podjetja TSMC in njihov fokus na pobude “Zero Defect” podčrtujejo osrednjo vlogo ultrapure testnih okolij v njihovi strategiji.

Paralelno z naložbami v livarno, glavni dobavitelji testne opreme, kot sta Advantest Corporation in Teradyne, Inc., hitro inovirajo, da bi ponudili rešitve za avtomatizirano testiranje (ATE) naslednje generacije, ki podpirajo testiranje redundance na procesnih vozliščih v nanometrskem merilu. Ti sistemi vse bolj izkoriščajo analitiko, ki jo poganja AI, in testiranje v višjih prepustnostih, da izboljšajo pokritost in zmanjšajo stopnje izpuščanja testov, kar zadostuje spremenjenim potrebam najnaprednejših tovarn.

Po nedavnih korporativnih razkritjih in industrijskih načrtih trga se pričakuje, da bo trg za opremo in storitve ultrapure testiranja redundance polprevodnikov rasel s letno obrestno mero (CAGR) v visokih enom digitih do leta 2030, pri čemer bo azijsko-pacifiška regija – ki jo prevladujejo Tajvan, Južna Koreja in Kitajska – ostala glavni motor povpraševanja. Širitev novih proizvodnih obratov (“mega fabs”) podjetij Samsung Electronics in TSMC v letih 2025–2027 dodatno podčrta robustno perspektivo sektorja.

V prihodnosti bo sprejem tehnologij ekstremne ultravijolične (EUV) litografije, heterogene integracije in arhitektur čipletov spodbudil še večje zanašanje na metodologije ultrapure testiranja redundance. Sodelovalna prizadevanja med proizvajalci, dobavitelji opreme in industrijskimi konsorci kot je SEMI naj bi pospešila razvoj standardov in najboljših praks, kar zagotavlja, da testiranje redundance sledi potrebam po rasti tehnologije in zanesljivosti do leta 2030 in naprej.

Ključni dejavniki: AI, IoT in napredno proizvodnjo vozlišč

Hitra evolucija umetne inteligence (AI), Interneta stvari (IoT) in napredne proizvodnje vozlišč močno pospešuje povpraševanje po ultrapure testiranju redundance polprevodnikov. Ko se kompleksnost naprav in gostota integracije povečujeta, še posebej pri vozliščih pod 5 nm, postane zagotavljanje odpornosti na napake in zanesljive delovanje ključnega pomena. Vse boljša testiranja redundance so, na primer, potrebna za dosego nizkih stopenj napak, ki so potrebne za kritične aplikacije v avtomobilskem, medicinskem in industrijskem sektorju. Intel Corporation in Taiwan Semiconductor Manufacturing Company poročata o naraščajočem fokusu na napredne sheme redundance in protokole testiranja za svoja najnovejša procesna vozlišča, kar odraža preusmeritev celotne industrije v smer izboljšane zanesljivosti.

Proliferacija IoT še dodatno povečuje potrebe po testiranju redundance. S milijardami medsebojno povezanih senzorjev in naprav, pričakovanih do leta 2025, morajo proizvajalci zagotavljati neprekinjeno delovanje in varnost, celo ob prisotnosti delnih okvar hardware. STMicroelectronics poudarja, da njihovi semiconductors, usmerjeni v IoT, skozi daljše testiranje redundance in zanesljivosti, z uporabo avtomatizirane testne opreme, ki je sposobna simulirati kompleksne načine okvar.

Uvedba arhitektur čipletov in 3D pakiranja na naprednih vozliščih prav tako spreminja metodologije testiranja. Kompleksni več-čipni sistemi zahtevajo ne le tradicionalne funkcionalne teste, temveč tudi preverjanje redundance na ravni sistema prek medsebojno povezanih čipov. Advanced Micro Devices (AMD) je sprejel nove strategije oblikovanja za test (DFT), ki upoštevajo redundanco za svoje procesorje na osnovi čipletov, medtem ko Synopsys in Advantest uvajata rešitve testiranja naslednje generacije, da bi ustrezali edinstvenim zahtevam po odpornosti na napake teh arhitektur.

- Podatki in trendi (2025 in naprej): Podjetja brez tovarn in livarne povečujejo svoje proračune za pokritje testov in presejanje redundance, s poročili o 18% letni rasti porabe za napredne testne naprave (ASML). Vstavitvene točke za testiranje waferjev in končnih paketov se širijo, še posebej za čipe, namenjene aplikacijam, usmerjenim v AI in kritični IoT.

- Napoved: V naslednjih letih se pričakuje, da bodo proizvajalci polprevodnikov še bolj sprejeli generacijo testnih vzorcev, ki jih poganja AI, in prilagodljive strategije redundance, kar bo zmanjšalo pobeg testov in izboljšalo zanesljivost na terenu. Integracija monitoringa redundance v realnem času v nameščene naprave – omogočena z robno AI in digitalnimi dvojniki – bo pomaknila meje odkrivanja in popravljanja napak na terenu (Infineon Technologies).

V povzetku, konvergenca AI, IoT in napredne proizvodnje vozlišč sili industrijo, da ponovno opredeli paradigme ultrapure testiranja redundance polprevodnikov, s pomembnimi naložbami in inovacijami napovedanimi do leta 2025 in naprej.

Ultrapure standardi: Spreminjajoče se zahteve in industrijski standardi

Testiranje redundance v ultrapure polprevodniških procesih postaja temeljna postavka proizvodnje polprevodnikov, saj se geometrije naprav še naprej zmanjšujejo in funkcionalna kompleksnost narašča. Potreba po zagotavljanju nemotene dobave ultrapure vode (UPW), kemikalij in plinov je povzročila nove standarde in merila za testiranje redundance po celotni industriji. V letu 2025 sektor pričakuje konvergenco strogih procesnih nadzorov, avtomatizacije in analitike podatkov, da bi ohranil te zahtevne zahteve.

Vodilni proizvajalci uvajajo večplastno redundanco v svoja ultrapure sistema za zmanjšanje tveganja kontaminacije ali izpadov. Na primer, Intel poroča, da zdaj njihove waferjeve tovarne uporabljajo dvo-vhodne UPW zanke, paralelne filtracijske sisteme in senzorje v realnem času, ki samodejno preklopijo na rezervne sisteme, če je zaznana odstopanja. Ta redundanca se nenehno testira s simulacijo in dejanji, kar zagotavlja, da lahko vse kritične točke ohranijo čistost na ravni polprevodnikov (<18 MΩ·cm za UPW) tudi v neprijaznih scenarijih.

Na strani oskrbe kemikalij podjetja, kot sta BASF in DuPont, sodelujejo s proizvajalci naprav za validacijo redundantne dostave in skladiščne infrastrukture. Ti sistemi se redno podvržejo preizkusom izzivov, kjer se prva oskrba namerno prekine, in avtomatsko preklapljanje na rezervne sisteme spremlja hitrost in zagotovitev čistoče. Podatki iz teh testov se delijo s strankami in so del preverjanj kakovosti dobaviteljev ter skladnosti z industrijskimi standardi, kot so SEMI F63 in smernice ITRS (SEMI).

Napoved za naslednja leta nakazuje tesnejša merila. Organizacija SEMI aktivno revizira svoje standarde za validacijo redundance, s poudarkom na digitalni sledljivosti, beleženju dogodkov in analitiki prediktivnih napak. Dobavitelji opreme, kot je Evoqua Water Technologies, zdaj ponujajo integrirane teste, ki združujejo fizične preizkuse preklapljanja z analitiko, ki temelji na oblaku, da bi omogočili neprekinjeno preverjanje.

Pritisk k pod-2 nm tehnologij proizvodnih procesov naj bi spodbujal še strožje protokole testiranja redundance. Izmenjava podatkov v realnem času med proizvajalci in dobavitelji, kot jo dokazujejo nedavne pobude TSMC, postaja standardna praksa. Ta sodelovalni pristop ne le povečuje odpornost, temveč zagotavlja tudi hitro reakcijo na anomalije, kar postavlja nove industrijske standarde zanesljivosti in celovitosti procesov v okolju, kjer lahko vsak prelom povzroči večmilijonske posledice.

Najnovejše inovacije v metodologijah testiranja redundance

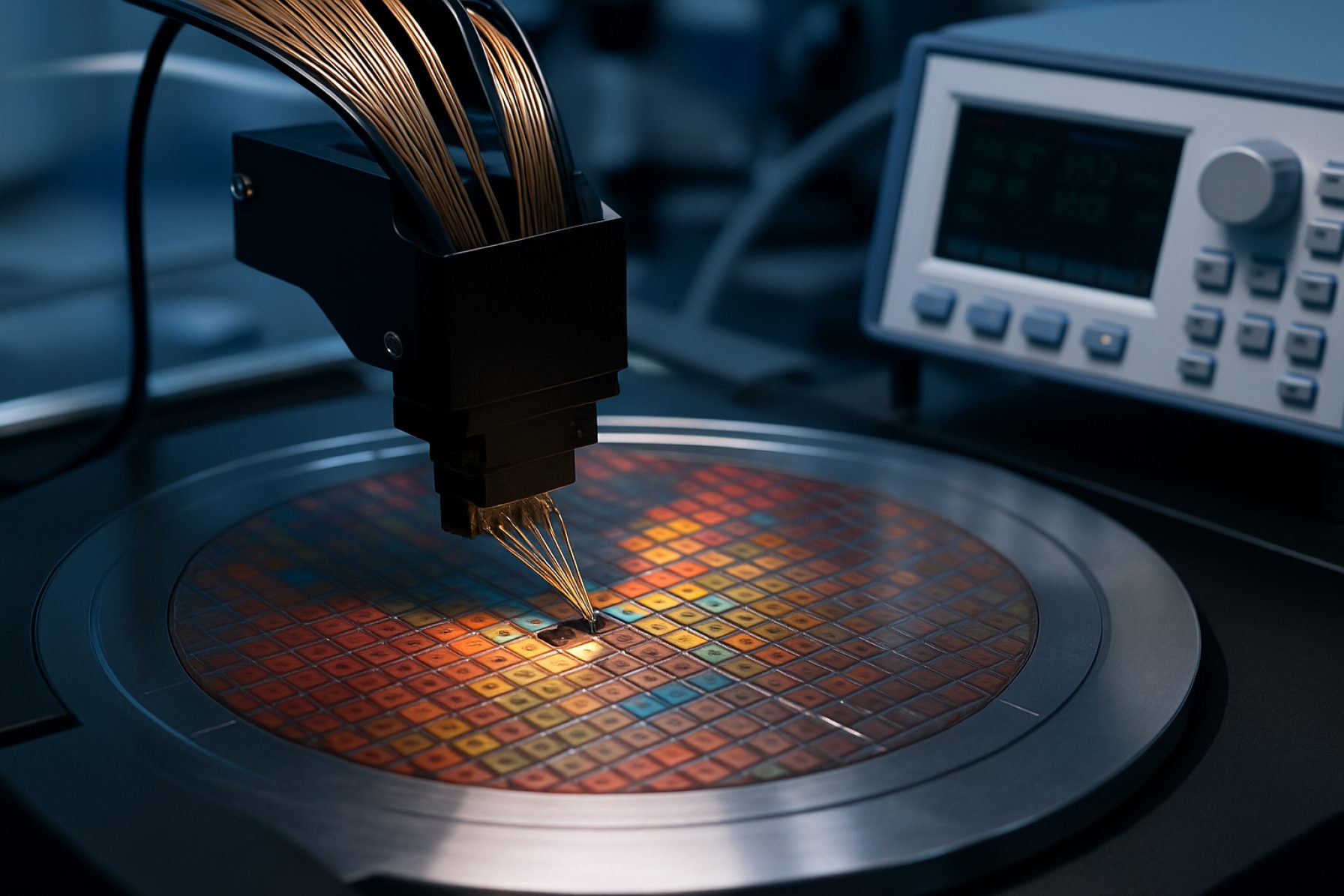

Ultrapure proizvodnja polprevodnikov še naprej premika meje zmogljivosti naprav, pri čemer se metodologije testiranja redundance hitro razvijajo, da bi zagotovile zanesljivost v vedno bolj kompleksnih integriranih vezjih (IC). Ko se geometrije naprav zmanjšujejo in se povečuje zahteva po ultra-visokih donosih, je testiranje redundance – zlasti za pomnilniške matrice in logiko – postalo osrednja točka inovacij.

V letu 2025 vodilni proizvajalci polprevodnikov uvajajo napredne rešitve za analizo in popravilo redundance, integrirane v svoje teste. Na primer, podjetje Taiwan Semiconductor Manufacturing Company (TSMC) je poudarilo uporabo prilagodljivih algoritmov redundance v svojih 3nm in 2nm procesnih vozliščih, ki izkoriščajo podatke o testiranju na kraju samem in strojno učenje za dinamično lokalizacijo napak in dodelitev rezervnih celic. Ta pristop zmanjšuje prekomerno obremenitev in podhranjenost, kar povečuje donos in dolgoročno zanesljivost.

Pri pomnilniških izdelkih je podjetje Samsung Electronics uvedlo oceno redundance v realnem času v svojih najnovejših DRAM in NAND flash proizvodnih linijah. Napredni krogi za samopopravljanje (BISR), podprti s prediktivno analitiko, omogočajo hitro identifikacijo in zamenjavo okvarjenih celic med razvrščanjem waferjev, tudi ko velikosti matrik presegajo stotine gigabitov. Te inovacije zmanjšujejo tveganje latentnih napak po namestitvi in optimizirajo uporabo redundantnih elementov na čipu.

Dobavitelji avtomatizirane testne opreme (ATE), kot je Advantest Corporation, uvajajo nove platforme z naravno podporo za protokole testiranja, ki upoštevajo redundanco. Njihova serija V93000, predstavljena leta 2024, omogoča testiranje v vzporedju in in-situ popravila za več-čipne pakete in čiplete – ključna funkcija, saj se napredno pakiranje razvija v visokozmogljivi računalništvu in aplikacijah umetne inteligence.

Ekosistem opreme za polprevodnike prav tako reagira na potrebo po ultrav čistem testnem okolju. Podjetje Lam Research poroča o napredku pri obvladovanju kontaminacij pri ravnanju z wafri in procesnimi komorami leta 2025, kar neposredno podpira celovitost testiranja redundance za napredna vozlišča, kjer lahko celo atomarne nečistoče izkrivljajo podatke o donosu ali skrivajo latentne napake redundance.

Ob pogledu naprej se pričakuje, da bo kombinacija analitike podatkov, so-optimizacije strojne in programske opreme ter strožjega nadzora procesov še naprej izboljšala testiranje redundance. Integracija digitalnih dvojnikov in napovedovanje napak, ki jih poganja AI, je na obzorju, kar obeta skoraj popolno proizvodnjo brez napak, ko se kompleksnost naprav povečuje. Sodelovanje med livarnami, proizvajalci opreme in oblikovalci brez tovarn bo ključno za uresničitev teh napredkov in ohranitev oskrbe z ultrapure, ultra-zanesljivimi polprevodniki.

Glavni akterji in strateška zavezništva (osredotočenost na 2025)

V letu 2025 je pokrajina testiranja redundance za ultrapure polprevodniške procese značilna po pomembnih aktivnostih med glavnimi igralci v industriji, strateškimi partnerstvi in investicijah v napredne testne rešitve. Ker se vozlišča za proizvodnjo polprevodnikov še naprej zmanjšujejo, je povpraševanje po ultrapure okoljih in robustnem testiranju redundance intenziviralo. Ključni igralci – vključno s proizvajalci opreme, livarnami polprevodnikov in dobavitelji materialov – vse bolj sodelujejo, da bi se spopadli s strogimi zahtevami po odkrivanju napak in zanesljivosti procesov.

- Applied Materials, Inc. ostaja na vrhu, saj ponuja napredne inšpekcijske in metrologijske platforme, ki omogočajo testiranje redundance na nanometrskih ravneh. V letu 2025 je podjetje napovedalo širitev sodelovanja z vrhunskimi proizvajalci logike in pomnilnika za skupni razvoj modulov za inšpekcijo redundance, optimiziranih za ultrapure okolja (Applied Materials, Inc.).

- ASML Holding NV še naprej igra ključno vlogo, zlasti prek svojih sistemov EUV litografije, ki zahtevajo rigorozno in-line testiranje redundance, da se zagotovi operativna stabilnost. Na začetku leta 2025 je ASML razširil svoje zavezništvo z vodilnimi proizvajalci čipov, da bi integriral lastne rutine testiranja redundance v orodja EUV, da bi zminimaliziral kontaminacijo in nepredvidene izpade (ASML Holding NV).

- Tokyo Electron Limited (TEL) je poglobil svoja partnerstva z globalnimi livarnami in podjetji brez tovarn ter se osredotočil na so-innovacije za ultrapure procesne module in preverjanje redundance. Iniciative podjetja TEL v letu 2025 vključujejo skupne pilotne programe z glavnimi fab obratih v Aziji za izpopolnitev avtomatiziranih testnih algoritmov za kritično upravljanje donosa (Tokyo Electron Limited).

- Samsung Electronics in TSMC – kot največji proizvajalci polprevodnikov na svetu – sta oba investirala v inovacije testiranja redundance znotraj svojih sistemov. V letu 2025 je Samsung napovedal implementacijo platforme za spremljanje redundance, ki jo poganja AI, v svojih naprednih logičnih linijah, medtem ko je TSMC razširil svoj program kvalifikacije redundance več dobaviteljev, da bi vključil nove testne protokole za 2 nm procesna vozlišča (Samsung Electronics; TSMC).

- Industrijska zavezništva, kot tista, ki jih usklajuje SEMI, so dodatno pospešila usklajevanje standardov testiranja in najboljših praks, pri čemer se nove delovne skupine v letu 2025 osredotočajo posebej na preverjanje redundance v ultrapure proizvodnih okoljih (SEMI).

V prihodnosti se pričakuje, da bo sektor doživel nadaljnje konvergiranje med dobavitelji opreme in proizvajalci naprav, pri čemer se bodo strateška zavezništva vse bolj osredotočila na so-razvoj prilagojenih testnih rešitev redundance. Ta sodelovalni pristop bo verjetno podlaga za naslednji val inovacij v ultrapure proizvodnji polprevodnikov, kar zagotavlja tako višje donose kot izboljšano zanesljivost naprav do leta 2026 in naprej.

Integracija dobavne verige in izzivi čistoče

Testiranje redundance v ultrapure polprevodnikih postaja ključni vidik integracije dobavne verige, saj se industrija polprevodnikov sooča z vedno strožjimi zahtevami po čistoči in naraščajočo kompleksnostjo proizvodnih procesov. Ker se geometrije čipov zmanjšujejo in občutljivost naprav na kontaminante povečuje, postaja zagotavljanje zanesljivosti in čistoče tako materialov kot končnih izdelkov skozi testiranje redundance tako tehnično kot logistično izziv.

V letu 2025 je poudarek na integraciji naprednih protokolov testiranja redundance po celotni dobavni verigi. Velike livarne in dobavitelji materialov zdaj zahtevajo večstopenjsko testiranje ultrapure plinov, kemikalij in silikonskih waferjev na različnih obdelovalnih vozliščih, da bi zmanjšali tveganje za uvajanje napak, povezanih z neodkritimi kontaminanti. Na primer, Intel Corporation je oblikoval strategije za redundantno inline in končno testiranje procesnih kemikalij, da bi zagotovil hitro odkrivanje in izolacijo napak ali kontaminacije na katerikoli točki, preden vplivajo na širše donose proizvodnje.

Drug ključni razvoj je sodelovalni pritisk za standardizacijo metrik čistoče in metodologij testiranja s strani industrijskih teles, kot je SEMI. V letih 2024 in 2025 je SEMI-jev program mednarodnih standardov sodeloval s proizvajalci čipov, dobavitelji opreme in trgovci s kemikalijami za izpopolnitev protokolov za redundanto validacijo čistoče, vključno z dvojno verifikacijo serij kemikalij in spremljanjem plinskih tokov v realnem času. Takšna prizadevanja neposredno obravnavajo integracijo dobavne verige z vzpostavljanjem enotnih pričakovanj in zahtev po delitvi podatkov med dobavitelji in proizvajalci.

Vodilni dobavitelji materialov, kot sta Entegris in DuPont, vlagajo v napredne senzorjske mreže in avtomatizirano analitiko za omogočanje nenehnih redundantnih preverjanj čistoče. Ti sistemi lahko sledijo kontaminantom do nivojev delcev na trilijon, kar zagotavlja uporabne podatke, ki se delijo z downstream partnerji kot del integriranega okvira zagotavljanja kakovosti. To je še posebej ključnega pomena, saj industrija gleda proti pod-2nm procesnim vozliščem, kjer lahko celo sledi nečistoč ogrozijo celovitost naprav.

V prihodnosti se pričakuje, da bo testiranje redundance postalo ne samo bolj avtomatizirano, temveč tudi globlje integrirano v digitalne sisteme upravljanja dobavne verige. Podjetja razvijajo rešitve za sledljivost, ki temeljijo na blockchainu, in varne platforme za deljenje podatkov, da bi zabeležila in potrdila vsak rezultat testa čistoče skozi dobavno verigo, kot to testira TSMC in njegovi partnerski ekosistemi. Ta digitalizacija bo pomagala identificirati morebitne okvare ali pomanjkljivosti v redundanci, preden lahko vplivajo na proizvodnjo velikih količin, kar bo dodatno varovalo čistočo in zanesljivost naprednih polprevodnikov.

Regulativno okolje in standardne organizacije (npr. SEMI.org, IEEE.org)

Regulativna pokrajina za ultrapure testiranje redundance polprevodnikov se hitro razvija, saj se industrija sooča z napredkom tehnologije in naraščajočimi zahtevami za zanesljivost naprav. Ultrapure okolja so ključna za proizvodnjo polprevodnikov, pri čemer tudi najmanjša kontaminacija ogroža neuspeh waferjev ali latentne napake naprav. Testiranje redundance – izvajanje več testnih metodologij ali rezervnih sistemov – je postalo osredotočeno na zagotavljanje, da so sami procesi testiranja dovolj robustni za odkrivanje in omilitev mogočih napak.

Ključne organizacij za razvoj standardov, kot sta SEMI in IEEE, igrajo vodilno vlogo pri oblikovanju regulativnega okolja za testiranje redundance. Na primer, standard SEMI F63 obravnava smernice za kakovost ultrapure vode (UPW) v proizvodnji polprevodnikov, kar posredno vpliva na protokole redundance tako, da določa meje tveganja kontaminacije in zahteve za spremljanje. V letu 2025 SEMI nadaljuje z osvežitvijo standardov, povezanih s testiranjem in nadzorom UPW in plinskih sistemov, ki so ključni za strategije redundance v kritičnih procesnih korakih.

Podobno ima IEEE stalne pobude znotraj svoje zdruge standardov, ki so pomembne za ponovljivost testnih metod, odpornost sistemov na napake ter redundanco pri kvalifikaciji polprevodniških naprav. IEEE 1687 (IJTAG) in sorodni standardi prispevajo k okvirjem za dostop do vgrajenih instrumentov za nadzor redundance in napak v realnem času. Ko postajajo naprave vse bolj kompleksne in se procesna vozlišča zmanjšujejo, testi standarde vedno bolj poudarjajo redundanco ne le v testnih rutinih, temveč tudi v arhitekturah samostojnega testa na čipu (BIST).

V zadnjih letih so globalni regulativni organi in industrijski konsorcije izpostavili usklajevanje najboljših praks. Program mednarodnih standardov SEMI na primer olajšuje čezmejno usklajevanje zahteve spremljanja in validacije redundance, kar odraža globalizirano naravo dobavnih verig polprevodnikov. V letu 2025 se tehnični odbori SEMI osredotočajo na sodelovanje z regionalnimi oblastmi, da bi zagotovili, da protokoli testiranja redundance ustrezajo tako lokalnim regulativnim zahtevam kot mednarodnim standardom.

V prihodnjih letih se pričakuje nadaljnje zaostrovanje regulativnega okolja. Ob proliferaciji aplikacij z visoko zanesljivostjo – kot so avtomobilska, letalska in zdravstvena elektronika – oblastniki verjetno zahtevajo še strožje protokole testiranja redundance in dokumentacijo. Odbori za standarde, kot sta SEMI in IEEE, naj bi izdali nove smernice, ki se nanašajo na napredne metode validacije redundance, pri čemer naraščajo zahteve po digitalni sledljivosti, prediktivni analitiki in nadzoru testiranja, ki ga poganja AI. Dejavnosti vseh deležnikov v industriji bo treba prilagoditi, da se proaktivno prilagodijo tem razvijajočim se standardom in ohranijo skladnost ter konkurenčno prednost.

Novi trgi in regionalne priložnosti

Pokrajina testiranja redundance za ultrapure polprevodnike se hitro spreminja v letu 2025, oblikovana z globalno širitvijo naprednega proizvodnje čipov ter rastočo kompleksnostjo integriranih vezij. Ko velike livarne vlagajo v vozlišča naslednje generacije – kot so 3nm in nižje – narašča povpraševanje po strogih protokolih testiranja redundance v ultrapure okolju, še posebej v novih središčih za proizvodnjo polprevodnikov.

V letu 2025 opazimo pomembno rast v azijsko-pacifiški regiji, pri čemer Tajvan, Južna Koreja in celinska Kitajska vodijo naložbe v novo zmogljivost fabov. Podjetja Taiwan Semiconductor Manufacturing Company (TSMC) in Samsung Electronics širita svoje napredne procesne zmogljivosti z močno osredotočenostjo na zmanjšanje kontaminacije in zagotavljanje redundance v kritičnih procesnih korakih. Ta podjetja integrirajo napredno testiranje redundance, da bi izpolnila vedno strožje standarde za napakovitost in zanesljivost, zlasti pri avtomobilskih in čipih, usmerjenih na AI.

Medtem ZDA beležijo oživitev v proizvodnji polprevodnikov, ki jo spodbuja zvezna spodbuda in partnerstva z lokalnimi dobavitelji. Intel aktivno gradi nove obrate v Arizoni in Ohiu, s poudarkom na uvajanju sistemov testiranja redundance za ultravijoč procesne tokove. Ti sistemi izkoriščajo inline inšpekcijo napak in analitiko v realnem času za odkrivanje in obvladovanje potencialnih enakovrednih točk okvar, s čimer izboljšajo donose in zanesljivost za kritične aplikacije.

V Evropi se pojavljanje novih objektov podjetja GlobalFoundries in nadaljnja rast podjetja Infineon Technologies povečujeta povpraševanje po napreden testiranja redundance. “Chips Act” Evropske unije si prizadeva za podvojitev proizvodnje čipov v regiji do leta 2030, kar spodbuja naložbe v ultrapure vodo, pline in tehnologije za obvladovanje kontaminacije, ki so odvisne od robustnega testiranja redundance za izpolnitev strogih kakovostnih zahtev.

Dobavitelji tehnologij, specializirani za testiranje redundance – kot sta Advantest Corporation in Teradyne – poročajo o povečanih naročilih tako od uveljavljenih fabov kot od novih vstopnikov v teh regijah. Njihove rešitve so vse bolj prilagojene visokoprehodnim, realnočasovnim odkrivanjem ultra-nizkonivoških kontaminantov in latentnih napak, pri čemer se pričakuje, da bodo analize, ki jih poganja AI, postale standard v naslednjih nekaj letih.

Ob pogledu naprej se novi trgi v jugovzhodni Aziji, Indiji in na Bližnjem vzhodu pripravljajo na razvoj svojih naprednih ekosistemov proizvodnje. Ko ta območja povečajo kapacitete, bo povpraševanje po ultrapure testiranju redundance intenziviralo, kar bo spodbujalo globalno sodelovanje ter sprejemanje najboljših tehnologij, da bi zagotovili dosledno kakovost in donose ob naraščajoči kompleksnosti čipov.

Strateški pregled: Motilne tehnologije in dolgoročni trendi

Testiranje redundance v ultrapure polprevodnikih je na vrhu zagotavljanja zanesljivosti, saj se geometrije naprav še naprej zmanjšujejo in kompleksnost tovarn narašča. Do leta 2025 bi moral strateški pregled tega področja biti močno oblikovan s konvergenco motilnih tehnologij in industrijskih sprememb v smeri proizvodnje brez napak, ki jo kroji povpraševanje po AI, avtomobilih in naprednih logičnih aplikacijah.

Voditelji proizvajalci polprevodnikov hitro razvijajo svoje metodologije testiranja redundance, da bi izpolnili višje standarde čistoče in donosa. Na primer, TSMC je poudaril svojo zavezo k naprednemu povečanju donosa in strogemu odkrivanju napak v svojih najnovejših procesnih tehnologijah, integrira inline testiranje redundance in analitiko, ki jo poganja AI, neposredno v svoje proizvodne linije. Podobno Intel vlaga v sistemom za validacijo redundance v realnem času, ki izkoriščajo strojno učenje za napovedovanje in izolacijo latentnih napak v njihovih procesnih tokovih 18A in 20A.

Pomemben trend v letu 2025 je sprejemanje naprednih metrologijskih in inšpekcijskih orodij, ki so sposobna odkrivati atome na ravni napak v ultrapure okolju. Podjetja Applied Materials in Lam Research, med vodilnimi dobavitelji opreme za polprevodnike na svetu, uvajajo platforme za inšpekcijo, ki združujejo e-beam slikanje, globoko učenje in delovne tokove, ki upoštevajo redundanco, da zagotovijo hitro zadržanje in popravilo procesnih odstopanj. Ti sistemi lahko detektirajo in karakterizirajo sub-nanometrske kontaminacije in električne napake, ki so ključnega pomena pri validaciji redundance za pomnilniške in logične čipe.

Drug motilni trend je integracija testiranja redundance v pametne platforme proizvodnje. Samsung Semiconductor testira spremljanje redundance, ki ga poganja AI, integrirano z digitalnimi dvojniki svojih tovarn, kar omogoča prediktivno vzdrževanje in takojšnjo recalibracijo procesov. To zmanjšuje izpade in povečuje zanesljivost proizvodnje naprednih vozlišč, kar neposredno obravnava pričakovanja o ničelnih napakah pri avtomobilih in podatkovnih centrih.

Gledano naprej, strateški pregled testiranja redundance v ultrapure polprevodnikih vključuje nadaljnjo avtomatizacijo in analitiko podatkov v oblaku. Industrijski konsorci, kot je SEMI, postavljajo nove standarde za interoperabilnost testnih protokolov in deljenje podatkov po celotni dobavni verigi, s ciljem racionalizirati verifikacijo redundance od waferja do sistemske ravni. Ko tovarne povečajo svoje zanašanje na napredno testiranje redundance, pričakujte nadaljnja sodelovanja med proizvajalci opreme, proizvajalci čipov in dobavitelji materialov, da pospešite odpravo napak v zaprtem krogu in potisnete meje zanesljivosti naprav do leta 2025 in naprej.

Viri in reference

- imec

- Advantest Corporation

- STMicroelectronics

- Synopsys

- ASML

- Infineon Technologies

- BASF

- DuPont

- Tokyo Electron Limited

- Samsung Electronics

- Entegris

- IEEE