Inhaltsverzeichnis

- Zusammenfassung: 2025 und der Weg nach vorne

- Marktgröße und Wachstumsausblicke bis 2030

- Schlüsseltreiber: KI, IoT und fortschrittliche Fertigungstechnologien

- Ultrapure Standards: Wandelnde Anforderungen und Branchenbenchmarks

- Neueste Innovationen in der Redundanzprüfung

- Wichtige Akteure und strategische Allianzen (Schwerpunkt 2025)

- Integration der Lieferkette und Herausforderungen bei der Reinheit

- Regulatorisches Umfeld und Normungsorganisationen (z.B. SEMI.org, IEEE.org)

- Schwellenmärkte und regionale Möglichkeiten

- Strategische Ausrichtung: Disruptive Technologien und langfristige Trends

- Quellen & Referenzen

Zusammenfassung: 2025 und der Weg nach vorne

Ultrapure Redundanzprüfungen in der Halbleiterindustrie gewinnen in der Übergangsphase zu 2025 an entscheidender Bedeutung, getrieben durch den unaufhörlichen Druck nach kleineren Knoten, höherer Gerätezuverlässigkeit und der Zunahme fortschrittlicher Anwendungen wie KI, automobile Elektronik und Quantencomputing. Ultrapure Umgebungen sind unerlässlich, um die strengen Ertrags- und Zuverlässigkeitsanforderungen von Sub-5nm und der nächsten Generation von Chipfertigung zu erreichen. Redundanzprüfungen – bei denen Backup-Schaltkreise und fehlertolerante Architekturen systematisch überprüft werden – sind zu einem entscheidenden Faktor geworden, um die Produktionsresilienz sicherzustellen, kostenintensive Ausfallzeiten zu minimieren und latente Defekte zu beheben, die selbst aus winzigen Verunreinigungen oder Prozessvariationen resultieren können.

Führende Halbleiterhersteller steigern ihre Investitionen in Redundanzprüfungen innerhalb ultrapurer Umgebungen. So erweitert die Taiwan Semiconductor Manufacturing Company (TSMC) weiterhin ihren Fokus auf die Validierung von Redundanzen im Rahmen ihrer Strategien zur fortschrittlichen Prozesskontrolle und Fehlerverwaltung, insbesondere bei ihren 3nm- und 2nm-Knoten. Ähnlich hat Samsung Electronics Semiconductor die Integration von Redundanzmechanismen und ausgeklügelten Testprotokollen in ihren hochmodernen Fabriken hervorgehoben, um die Gerätezuverlässigkeit weiter zu stärken, während sie auf Gate-All-Around (GAA) Transistorarchitekturen umschalten.

Ausrüstungsanbieter passen sich ebenfalls diesen Anforderungen an. Applied Materials und Lam Research entwickeln innovative Wafer-Inspektions- und Messtechnik-Tools, die KI-gesteuerte Analytik nutzen, um Redundanzfehler effizienter in ultrapuren Prozesslinien zu erkennen und zu charakterisieren. Diese Systeme werden eingesetzt, um prozessbedingte Defektraten zu überwachen und die betriebliche Integrität redundanter Strukturen zu validieren.

Daten von Branchenkonsortien wie SEMI zeigen, dass die Investitionen in Test- und Messtechnik für fortschrittliche Redundanzsysteme bis 2028 voraussichtlich mit einer jährlichen Wachstumsrate (CAGR) von über 7 % zunehmen werden, was die Priorisierung des Sektors für Ertragsmanagement und Zuverlässigkeitssicherung widerspiegelt. Darüber hinaus beschleunigen kollaborative Bemühungen wie die bei imec die Entwicklung neuartiger Redundanzarchitekturen und Fertigungsprotokolle, die auf ultrapure Umgebungen zugeschnitten sind.

In den kommenden Jahren wird Redundanzprüfung voraussichtlich zunehmend automatisiert, datenorientiert und eng in die Echtzeit-Prozesskontrolle integriert. Während die Halbleiterhersteller auf 2nm und darüber hinaus zusteuern, wird das Null-Fehler-Paradigma von Fortschritten sowohl im Redesign als auch bei der Prüfung innerhalb ultrapurer Umgebungen abhängen. Diese Evolution wird entscheidend sein, um die Zuverlässigkeit, Skalierbarkeit und kommerzielle Lebensfähigkeit zukünftiger Halbleitertechnologien aufrechtzuerhalten.

Marktgröße und Wachstumsausblicke bis 2030

Der globale Markt für ultrapure Redundanzprüfungen in der Halbleiterindustrie steht bis 2030 vor einem signifikanten Wachstum, das durch die zunehmende Komplexität der Halbleitergeräte, die Verbreitung fortschrittlicher Knoten (5nm, 3nm und darunter) und die steigende Nachfrage nach ultrazuverlässigen Chips in kritischen Anwendungen wie Automobil, Rechenzentren und KI vorangetrieben wird. Da sich die Geometrien der Geräte verkleinern und die Integrationsgrade steigen, hat die Notwendigkeit, absolute Reinheit und Robustheit in den Fertigungsprozessen von Halbleitern sicherzustellen, die Redundanzprüfung an die Spitze der Qualitätssicherung gestellt.

Im Jahr 2025 werden führende Halbleiterhersteller wie die Taiwan Semiconductor Manufacturing Company (TSMC), Samsung Electronics und Intel Corporation ihre Investitionen in fortschrittliche Infrastrukturen für Redundanzprüfungen weiterhin ausbauen. Diese Investitionen zielen nicht nur darauf ab, latente Defekte in Logik- und Speicher-Schaltkreisen zu erkennen und zu beseitigen, sondern auch die immer strengeren Zuverlässigkeitsanforderungen zu erfüllen, die von Automobil- und missionskritischen Sektoren gefordert werden. TSMCs laufende Kapazitätserweiterungen und ihr Fokus auf „Zero Defect“-Initiativen verdeutlichen die zentrale Rolle von ultrapuren Testumgebungen in ihrem Fahrplan.

Parallel zu den Investitionen in Foundries innovieren große Anbieter von Testgeräten wie Advantest Corporation und Teradyne, Inc., um Lösungen für automatisierte Testgeräte (ATE) der nächsten Generation bereitzustellen, die Redundanzprüfungen bei nanometergenauen Prozessknoten unterstützen können. Diese Systeme nutzen zunehmend KI-gesteuerte Analytik und Hochdurchsatz-Paralleltests, um die Abdeckung zu verbessern und die Prüfentkommenraten zu reduzieren und den sich wandelnden Bedürfnissen führender Fabriken gerecht zu werden.

Laut kürzlichen Unternehmensangaben und Branchenausblicken wird der Markt für ultrapure Redundanzprüfungsgeräte und -dienstleistungen voraussichtlich bis 2030 mit einer jährlichen Wachstumsrate (CAGR) im hohen einstelligen Bereich wachsen, wobei die Region Asien-Pazifik – dominiert von Taiwan, Südkorea und China – die Hauptquelle der Nachfrage bleibt. Die Expansion neuer Fertigungsanlagen („Mega-Fabs“) durch Samsung Electronics und TSMC in 2025–2027 unterstreicht die robuste Perspektive des Sektors.

In den kommenden Jahren wird die Übernahme fortschrittlicher ultravioletter (EUV) Lithographie, heterogener Integration und Chiplet-Architekturen auch zu einer noch stärkeren Abhängigkeit von ultrapuren Redundanzprüfmethoden führen. Zusammenarbeit zwischen Herstellern, Ausrüstungsanbietern und Branchenkonsortien wie SEMI wird voraussichtlich die Entwicklung von Standards und Best Practices beschleunigen, um sicherzustellen, dass die Redundanzprüfung mit der Technologiedimensionierung und den Anforderungen an die Zuverlässigkeit bis 2030 und darüber hinaus Schritt hält.

Schlüsseltreiber: KI, IoT und fortschrittliche Fertigungstechnologien

Die rasante Entwicklung von Künstlicher Intelligenz (KI), Internet der Dinge (IoT) und fortschrittlicher Fertigungstechnologien beschleunigt die Nachfrage nach ultrapuren Redundanzprüfungen in der Halbleiterindustrie erheblich. Mit der steigenden Komplexität und Dichte der Integration von Geräten, insbesondere bei Knoten unter 5 nm, wird die Sicherstellung von Fehlertoleranz und zuverlässiger Leistung von entscheidender Bedeutung. KI-Beschleuniger erfordern beispielsweise nun robuste Redundanzprüfungen, um die niedrigen Defektraten zu erreichen, die für kritische Anwendungen in den Bereichen Automobil, Medizin und Industrie erforderlich sind. Intel Corporation und die Taiwan Semiconductor Manufacturing Company berichten beide von einem wachsenden Fokus auf fortschrittliche Redundanzsysteme und Prüfprotokolle für ihre neuesten Prozessknoten, was einen branchenweiten Trend zu verbesserter Zuverlässigkeit widerspiegelt.

Die Verbreitung von IoT verstärkt zudem die Anforderungen an Redundanzprüfungen. Mit Milliarden von vernetzten Sensoren und Geräten, die bis 2025 erwartet werden, müssen die Hersteller die kontinuierliche Betriebszeit und Sicherheit garantieren, selbst bei teilweisen Hardwareausfällen. STMicroelectronics hebt hervor, dass ihre auf IoT ausgerichteten Halbleiter umfassenden Redundanz- und Zuverlässigkeitsprüfungen unterzogen werden, wobei automatisierte Testgeräte genutzt werden, die in der Lage sind, komplexe Fehlermodi zu simulieren.

Die Einführung von Chiplet-Architekturen und 3D-Verpackungen bei fortschrittlichen Knoten transformiert ebenfalls die Prüfmethologien. Komplexe Multichip-Systeme erfordern nicht nur traditionelle Funktionstests, sondern auch systemweite Redundanzüberprüfungen über verbundene Chips hinweg. Advanced Micro Devices (AMD) hat neue, redundanzbewusste Design-for-Test (DFT) Strategien für seine chipletbasierten Prozessoren angenommen, während Synopsys und Advantest Lösungen der nächsten Generation entwickeln, um die einzigartigen Anforderungen an die Fehlertoleranz dieser Architekturen zu adressieren.

- Daten und Trends (2025 und darüber hinaus): Fabless Unternehmen und Foundries erhöhen ihre Testabdeckung und Budgets für Redundanzprüfungen, mit einem berichteten Wachstum von 18 % im Jahr für Ausgaben für fortschrittliche Testgeräte (ASML). Die Testeinsetzungen für Wafer und Endpackungen erweitern sich, insbesondere für Chips, die für KI- und sicherheitskritische IoT-Anwendungen bestimmt sind.

- Aussichten: In den nächsten Jahren wird erwartet, dass Halbleiterhersteller weiter KI-gesteuerte Testmuster-Generierung und adaptive Redundanzstrategien übernehmen, um Testfehler zu reduzieren und die Zuverlässigkeit im Feld zu verbessern. Die Integration von Echtzeit-Redundanzüberwachung in implizierbare Geräte – ermöglicht durch Edge-KI und digitale Zwillinge – wird die Grenzen der Fehlererkennung und -korrektur im Feld weiter verschieben (Infineon Technologies).

Zusammenfassend zwingt die Konvergenz von KI, IoT und fortschrittlicher Fertigungstechnologie die Branche dazu, die Paradigmen der ultrapuren Redundanzprüfung neu zu definieren, mit erheblichen Investitionen und Innovationen, die bis 2025 und darüber hinaus prognostiziert werden.

Ultrapure Standards: Wandelnde Anforderungen und Branchenbenchmarks

Ultrapure Redundanzprüfungen werden zu einem Grundpfeiler der Halbleiterfertigung, da sich die Gerätegeometrien weiter verkleinern und die funktionale Komplexität steigt. Die Notwendigkeit, eine ununterbrochene Versorgung mit ultrapurem Wasser (UPW), Chemikalien und Gasen sicherzustellen, hat neue Standards und Benchmarks für Redundanzprüfungen in der gesamten Branche hervorgebracht. Im Jahr 2025 beobachtet der Sektor eine Konvergenz von strenger Prozesskontrolle, Automatisierung und Datenanalytik, um diese hohen Anforderungen aufrechtzuerhalten.

Führende Hersteller setzen in ihren ultrapuren Systemen mehrschichtige Redundanzen ein, um Risiken von Kontamination oder Ausfallzeiten zu mindern. So berichtet Intel, dass ihre Wafer-Fabs nun auf doppelte UPW-Schleifen, parallele Filtrationsanlagen und Echtzeit-Sensoren setzen, um automatisch auf Backup-Systeme umzuschalten, wenn eine Abweichung festgestellt wird. Diese Redundanz wird kontinuierlich durch Simulation und Live-Übungen getestet, um sicherzustellen, dass alle kritischen Knoten die Halbleiterqualität (<18 MΩ·cm für UPW) selbst in schwierigen Szenarien aufrechterhalten können.

Auf der Seite der chemischen Versorgung arbeiten Unternehmen wie BASF und DuPont mit Geräteherstellern zusammen, um die redundante Lieferung und Lagerinfrastruktur zu validieren. Diese Systeme unterziehen sich regelmäßigen Herausforderungstests, wobei die primäre Versorgung absichtlich unterbrochen und der automatische Übergang zu Backup überwacht wird, um sowohl die Geschwindigkeit als auch die Garantie der Reinheit sicherzustellen. Die Daten aus diesen Tests werden mit den Kunden geteilt und bilden einen Teil der Qualitätsprüfungen der Lieferanten sowie der Einhaltung von Branchenstandards wie SEMI F63 und ITRS-Richtlinien (SEMI).

Die Aussichten für die nächsten Jahre weisen auf eine weitere Verschärfung der Benchmarks hin. Die SEMI-Organisation überarbeitet aktiv ihre Standards für die Validierung von Redundanzen, wobei der Schwerpunkt auf digitaler Rückverfolgbarkeit, Ereignisprotokollierung und prädiktiver Fehleranalyse liegt. Ausrüstungsanbieter wie Evoqua Water Technologies bieten jetzt integrierte Testpakete an, die physische Umschaltungstests mit cloudbasierten Diagnosen kombinieren, um kontinuierliche Prüfungen zu gewährleisten.

Der Druck hin zu sub-2nm-Prozesstechnologien wird voraussichtlich noch strengere Protokolle für Redundanzprüfungen vorantreiben. Der Austausch von Echtzeitdaten zwischen Herstellern und Lieferanten, wie ihn neueste Initiativen von TSMC zeigen, wird zum Standard. Dieser kollaborative Ansatz erhöht nicht nur die Resilienz, sondern sorgt auch für eine schnelle Reaktion auf Anomalien und setzt neue Branchenbenchmarks für Zuverlässigkeit und Prozessintegrität in einem Umfeld, in dem jede Lücke multimillionenschwere Folgen haben kann.

Neueste Innovationen in der Redundanzprüfung

Die ultrapure Halbleiterfertigung drängt weiterhin die Grenzen der Geräteleistung, während die Methoden der Redundanzprüfung sich schnell weiterentwickeln, um die Zuverlässigkeit in zunehmend komplexen integrierten Schaltungen (ICs) sicherzustellen. Mit der Verkleinerung der Gerätegeometrien und dem steigenden Bedarf an ultrahochem Ertrag hat sich die Redundanzprüfung – insbesondere für Speicherarrays und Logik – zu einem Innovationsschwerpunkt entwickelt.

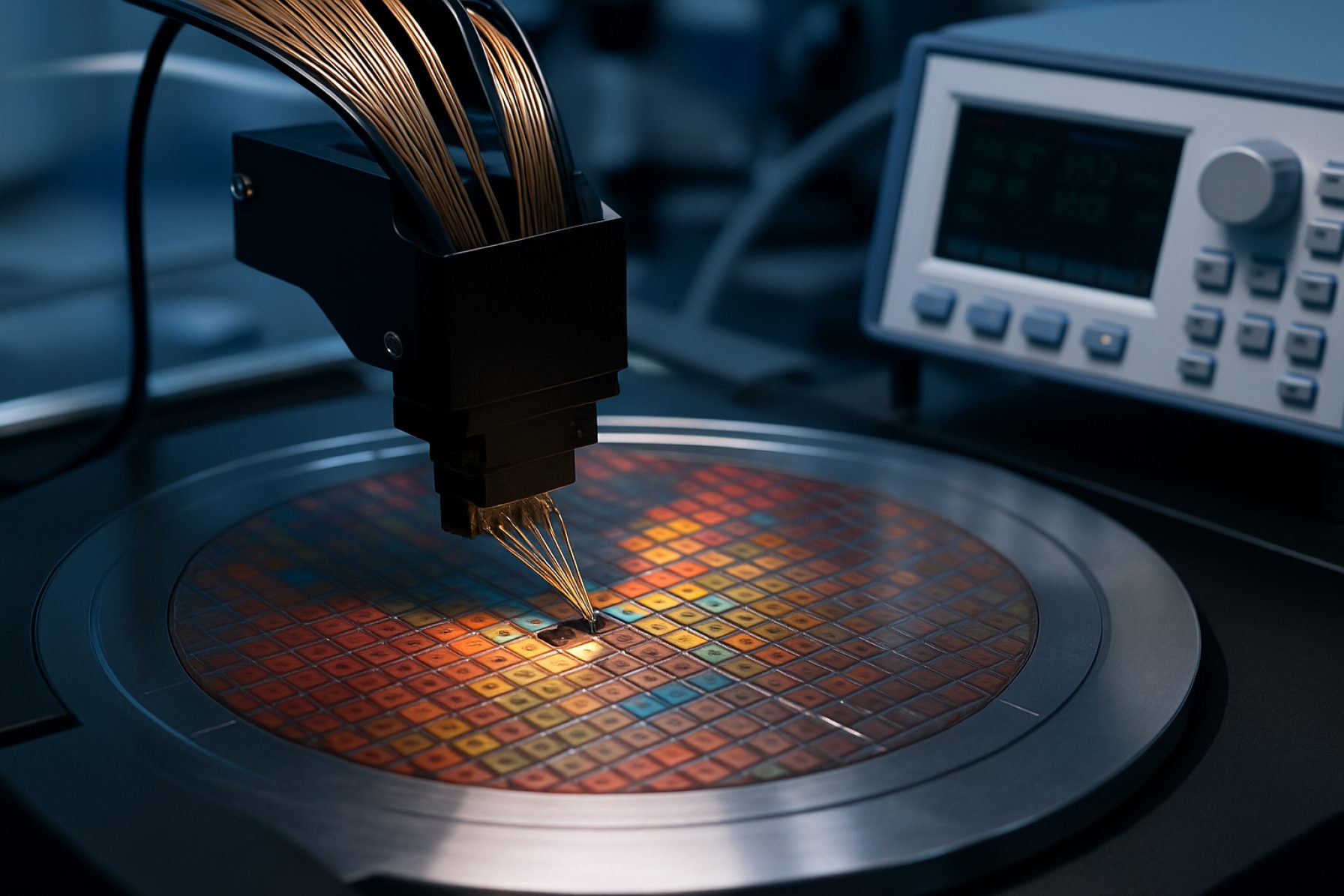

Im Jahr 2025 setzen führende Halbleiterhersteller fortschrittliche Redundanzanalyse- und Reparaturlösungen ein, die in ihre Testabläufe integriert sind. So hat die Taiwan Semiconductor Manufacturing Company (TSMC) die Anwendung adaptiver Redundanzalgorithmen in ihren 3nm- und 2nm-Prozessknoten hervorgehoben, indem sie Inline-Testdaten und maschinelles Lernen für dynamische Defektlokalisierung und Ersatzzellenzuweisung nutzt. Dieser Ansatz reduziert Über- und Unterkill und erhöht sowohl die Ausbeute als auch die langfristige Zuverlässigkeit.

Im Bereich der Speicherprodukte hat Samsung Electronics die Echtzeitbewertung der Redundanz in ihren neuesten DRAM- und NAND-Flash-Linien implementiert. Fortschrittliche eingebaute Selbstreparatur (BISR) Schaltungen, die durch prädiktive Analytik ergänzt werden, ermöglichen eine schnelle Identifizierung und den Austausch defekter Zellen während der Wafer-Sichtung, selbst wenn die Array-Größen Hunderte von Gigabits überschreiten. Diese Innovationen minimieren das Risiko latenter Fehler nach der Inbetriebnahme und optimieren die Nutzung der auf dem Chip vorhandenen redundanten Elemente.

Anbieter von automatisierten Testgeräten (ATE) wie Advantest Corporation führen neue Plattformen ein, die eine native Unterstützung für redundanzbewusste Testprotokolle bieten. Ihre V93000-Serie, die 2024 eingeführt wurde, ermöglicht paralleles Testen und In-situ-Reparaturen für Multichip-Pakete und Chiplets – ein wichtiges Merkmal, da fortschrittliche Verpackungen in Hochleistungscomputing- und Künstliche Intelligenz-Anwendungen zunehmen.

Das Ökosystem der Halbleitergeräte reagiert ebenfalls auf den Bedarf an ultrasauberen Testumgebungen. Lam Research berichtete 2025 von Fortschritten in der kontaminationsfreien Wafer-Handhabung und den Prozesskammern, die die Integrität von Redundanzprüfungen für hochmoderne Knoten unterstützen, bei denen selbst Verunreinigungen auf atomarer Ebene die Ausbeutedaten verfälschen oder latente Redundanzfehler verschleiern können.

Mit Blick auf die Zukunft wird eine Konvergenz von Datenanalytik, Hardware-Software-Co-Optimierung und strengerer Prozesskontrolle erwartet, die die Redundanzprüfung weiter verbessern wird. Die Integration von digitalen Zwillingen und KI-gesteuerter Fehlerprognose steht bevor und verspricht eine nahezu fehlerfreie Produktion, während die Komplexität der Geräte zunimmt. Die Zusammenarbeit zwischen Foundries, Geräteherstellern und fabless Designern wird entscheidend sein, um diese Fortschritte zu realisieren und die Versorgung mit ultrapuren, ultra zuverlässigen Halbleitern aufrechtzuerhalten.

Wichtige Akteure und strategische Allianzen (Schwerpunkt 2025)

Im Jahr 2025 wird die Landschaft für ultrapure Redundanzprüfungen in der Halbleiterindustrie durch erhebliche Aktivitäten unter wichtigen Branchenakteuren, strategischen Partnerschaften und Investitionen in fortschrittliche Testlösungen geprägt. Da die Fertigungstechnologien im Halbleitermarkt weiterhin schrumpfen, hat die Nachfrage nach ultrapuren Umgebungen und robusten Redundanzprüfungen zugenommen. Schlüsselakteure – einschließlich Gerätehersteller, Halbleiterfoundries und Materiallieferanten – arbeiten zunehmend zusammen, um die strengen Anforderungen an die Fehlererkennung und Prozesszuverlässigkeit zu erfüllen.

- Applied Materials, Inc. bleibt an der Spitze und bietet fortschrittliche Inspektions- und Messtechnikplattformen, die Redundanzprüfungen auf Nanometerebene ermöglichen. Im Jahr 2025 gab das Unternehmen Expansionen in seiner Zusammenarbeit mit führenden Logik- und Speicherherstellern bekannt, um die nächsten Generationen von Redundanzinspektionsmodulen zu entwickeln, die auf ultrapure Umgebungen optimiert sind (Applied Materials, Inc.).

- ASML Holding NV spielt weiterhin eine zentrale Rolle, insbesondere durch seine EUV-Lithographiesysteme, die strenge inline Redundanzprüfungen erfordern, um die operative Stabilität sicherzustellen. Anfang 2025 erweiterte ASML seine Allianz mit führenden Chipherstellern, um proprietäre Redundanz-Testverfahren in EUV-Werkzeugen zu integrieren, mit dem Ziel, Kontamination und ungeplante Ausfallzeiten zu minimieren (ASML Holding NV).

- Tokyo Electron Limited (TEL) hat seine Partnerschaften mit globalen Foundries und fabless Unternehmen vertieft und sich auf die Co-Innovation für ultrapure Prozessmodule und die Validierung von Redundanzen konzentriert. Die Initiativen von TEL im Jahr 2025 umfassen gemeinsame Pilotprogramme mit großen Fabs in Asien zur Verfeinerung automatisierter Testalgorithmen für das kritische Ertragsmanagement (Tokyo Electron Limited).

- Samsung Electronics und TSMC – als die größten Halbleiterhersteller der Welt – haben beide in interne Innovationen für Redundanzprüfungen investiert. Im Jahr 2025 gab Samsung die Implementierung einer KI-gesteuerten Redundanzüberwachungsplattform in seinen fortschrittlichen Logiklinien bekannt, während TSMC sein Multi-Vendor-Qualifizierungsprogramm für Redundanz um neue Testprotokolle für 2nm-Prozessknoten erweiterte (Samsung Electronics; TSMC).

- Branchenallianzen, wie die von SEMI koordinierten, haben die Harmonisierung von Teststandards und Best Practices weiter beschleunigt, wobei neue Arbeitsgruppen im Jahr 2025 speziell auf die Validierung von Redundanzen in ultrapuren Fertigungsumgebungen fokussiert sind (SEMI).

Blickt man in die Zukunft, wird erwartet, dass der Sektor weiterhin eine Konvergenz zwischen Geräteanbietern und Herstellern beobachten wird, wobei strategische Allianzen zunehmend auf die gemeinsame Entwicklung maßgeschneiderter, inline Redundanz-Testlösungen ausgerichtet sein werden. Dieser kollaborative Ansatz wird voraussichtlich die nächste Innovationswelle in der ultrapuren Halbleiterfertigung untermauern und sowohl höhere Erträge als auch verbesserte Gerätezuverlässigkeit bis 2026 und darüber hinaus gewährleisten.

Integration der Lieferkette und Herausforderungen bei der Reinheit

Ultrapure Redundanzprüfungen sind ein Schlüsselbestandteil der Integration der Lieferkette geworden, da die Halbleiterindustrie mit immer strikteren Reinheitsanforderungen und wachsender Komplexität in den Fertigungsprozessen konfrontiert ist. Mit dem Schrumpfen der Chipgeometrien und der zunehmenden Empfindlichkeit der Geräte gegenüber Verunreinigungen ist die Gewährleistung der Zuverlässigkeit und Reinheit von Materialien und Endprodukten durch Redundanzprüfungen sowohl eine technische als auch logistische Herausforderung geworden.

Im Jahr 2025 liegt der Fokus auf der Integration fortschrittlicher Redundanzprüfungsprotokolle entlang der Lieferkette. Wichtige Foundries und Materiallieferanten verlangen nun mehrstufige Tests ultrapurer Gase, Chemikalien und Silizium-Wafer an verschiedenen Bearbeitungsknoten, um das Risiko der Einführung von Defekten aufgrund undetected Kontaminationen zu minimieren. Intel Corporation hat beispielsweise Strategien zur redundanten Inline- und Endpunktprüfung von Prozesschemikalien skizziert, um sicherzustellen, dass Fehler oder Kontaminationen an irgendeinem Punkt schnell erkannt und isoliert werden, bevor sie breitere Produktionsausbeuten beeinträchtigen.

Eine weitere wichtige Entwicklung ist der kollaborative Vorstoß zur Standardisierung von Reinheitsmetriken und Testmethoden durch Branchenverbände wie SEMI. Im Jahr 2024 und bis 2025 arbeitet das SEMI-Programm für internationale Standards mit Chip-Herstellern, Ausrüstungsanbietern und Chemikalienherstellern zusammen, um Protokolle für die redundante Validierung der Reinheit zu verfeinern, einschließlich der Überprüfung von Dual-Source-Chemikalien und Echtzeitüberwachung von Gasströmen. Solche Initiativen richten sich direkt an die Integration der Lieferkette, indem sie einheitliche Erwartungen und Datenverbreitungsanforderungen zwischen Lieferanten und Herstellern festlegen.

Führende Materiallieferanten wie Entegris und DuPont investieren in fortschrittliche Sensornetzwerke und automatisierte Analytik, um kontinuierliche, redundante Reinheitsprüfungen zu ermöglichen. Diese Systeme können Verunreinigungen bis auf Teile pro Billionen erkennen und handlungsfähige Daten bereitstellen, die im Rahmen eines integrierten Qualitätssicherungsrahmens mit nachgelagerten Partnern geteilt werden. Dies ist besonders wichtig, da die Branche auf sub-2nm Prozessknoten zusteuert, bei denen selbst geringfügige Verunreinigungen die Integrität der Geräte gefährden können.

In den nächsten Jahren wird voraussichtlich gesehen werden, dass Redundanzprüfungen nicht nur automatisierter, sondern auch tiefer in digitale Systeme des Lieferkettenmanagements eingebettet werden. Unternehmen entwickeln blockchain-basierte Rückverfolgbarkeitslösungen und sichere Datenfreigabeplattformen, um jedes Testergebnis zu protokollieren und zu verifizieren, wie sie von TSMC und seinen Ecosystem-Partnern demonstriert werden. Diese Digitalisierung wird dazu beitragen, potenzielle Zusammenbrüche oder Lücken in der Redundanz zu identifizieren, bevor sie die Massenproduktion beeinträchtigen können, und die Reinheit und Zuverlässigkeit fortschrittlicher Halbleiter weiter zu schützen.

Regulatorisches Umfeld und Normungsorganisationen (z.B. SEMI.org, IEEE.org)

Die regulatorische Landschaft für ultrapure Redundanzprüfungen in der Halbleiterindustrie entwickelt sich schnell, da die Branche sowohl technologische Fortschritte als auch steigende Anforderungen an die Gerätezuverlässigkeit konfrontiert. Ultrapure Umgebungen sind für die Halbleiterfertigung von entscheidender Bedeutung, und selbst kleinste Verunreinigungen können das Versagen von Wafern oder latente Gerätefehler riskieren. Redundanzprüfungen – die Verwendung mehrerer Testmethoden oder Backup-Systeme – sind zu einem Schwerpunkt geworden, um sicherzustellen, dass die Prüfprozesse selbst robust genug sind, um mögliche Fehler zu erkennen und zu mindern.

Wichtige Organisationen zur Entwicklung von Standards wie SEMI und IEEE spielen eine treibende Rolle bei der Gestaltung des regulatorischen Umfelds für Redundanzprüfungen. Der SEMI F63 Standard behandelt beispielsweise Richtlinien für die Qualität von ultrapurem Wasser (UPW) in der Halbleiterfertigung und hat indirekt Auswirkungen auf Redundanzprotokolle, indem er Verunreinigungsrisikolimits und Überwachungsanforderungen festlegt. Im Jahr 2025 aktualisiert SEMI weiterhin Standards im Zusammenhang mit Tests und der Überwachung von UPW- und Gassystemen, die für Redundanzstrategien in kritischen Prozessschritten unerlässlich sind.

Ebenso hat die IEEE laufende Initiativen innerhalb ihrer Normungsorganisation, die sich auf die Wiederholbarkeit von Testmethoden, Fehlertoleranzsysteme und Redundanz in der Qualifizierung von Halbleitergeräten beziehen. IEEE 1687 (IJTAG) und verwandte Standards bieten Rahmenbedingungen für den Zugang zu eingebetteten Instrumenten zur Echtzeit-Redundanz- und Fehlermonitoring. Mit zunehmender Komplexität der Geräte und der Schrumpfung der Prozessknoten betonen Teststandards zunehmend Redundanz nicht nur in den Testabläufen, sondern auch in den integrierten Selbsttestarchitekturen (BIST) auf dem Chip.

In den letzten Jahren haben globale Regulierungsbehörden und Branchenkonsortien die Harmonisierung von Best Practices betont. Zum Beispiel erleichtert das internationale Standards-Programm von SEMI die grenzüberschreitende Abstimmung zu Überwachungsanforderungen und Redundanzvalidierung, die die globalisierte Natur der Halbleiterversorgungsketten widerspiegeln. Im Jahr 2025 priorisieren technische Komitees von SEMI die Zusammenarbeit mit regionalen Behörden, um sicherzustellen, dass die Protokolle zur Redundanzprüfung sowohl lokalen regulatorischen Anforderungen als auch internationalen Standards genügen.

In den nächsten Jahren wird voraussichtlich erwartet, dass das regulatorische Umfeld weiter verschärft wird. Mit der Verbreitung von Anwendungen mit hoher Zuverlässigkeit – wie Automobil-, Luft- und Raumfahrt- und Gesundheits Elektronik – werden die Behörden voraussichtlich strengere Redundanzprüfungen und Dokumentationen vorschreiben. Normungsorganisationen wie SEMI und IEEE werden voraussichtlich neue Richtlinien herausgeben, die fortschrittliche Methoden zur Verifizierung von Redundanzen adressieren, mit zunehmenden Anforderungen an digitale Nachverfolgbarkeit, prädiktive Analytik und KI-gesteuerte Testaufsicht. Die Akteure in der gesamten Industrie müssen agil bleiben und sich proaktiv an diese sich entwickelnden Standards anpassen, um die Konformität und den Wettbewerbsvorteil aufrechtzuerhalten.

Schwellenmärkte und regionale Möglichkeiten

Die Landschaft für ultrapure Redundanzprüfungen in der Halbleiterindustrie entwickelt sich 2025 schnell, geprägt durch die globale Expansion der fortschrittlichen Chipfertigung und die zunehmende Komplexität integrierter Schaltungen. Da große Foundries in nächste Generationen von Knoten – wie 3nm und darunter – investieren, steigt die Nachfrage nach strengen Redundanzprüfungsprotokollen in ultrapuren Umgebungen, insbesondere in aufstrebenden Halbleiterfertigungshubs.

Im Jahr 2025 wird in der Region Asien-Pazifik ein signifikantes Wachstum beobachtet, wobei Taiwan, Südkorea und das chinesische Festland die Investitionen in neue Fertigungskapazitäten anführen. Die Taiwan Semiconductor Manufacturing Company (TSMC) und Samsung Electronics erweitern ihre fortschrittlichen Prozessfähigkeiten mit einem starken Fokus auf die Minimierung von Kontamination und die Sicherstellung von Redundanz in kritischen Prozessschritten. Diese Unternehmen integrieren fortschrittliche Redundanzprüfungen, um den ständig strenger werdenden Anforderungen an Defektivität und Zuverlässigkeit, insbesondere bei Automobil- und KI-zentrierten Chips, gerecht zu werden.

In den USA wird ein Wiederaufschwung in der Halbleiterfertigung beobachtet, angetrieben durch staatliche Anreize und Partnerschaften mit lokalen Anbietern. Intel baut aktiv neue Fabriken in Arizona und Ohio und legt dabei Wert auf die Implementierung von Redundanzprüfungssystemen für ultrapure Produktionsströme. Diese Systeme nutzen inline Defektinspektionen und Echtzeitanalytik zur Erkennung und Minderung potenzieller einzelner Fehlerquellen und verbessern somit die Ausbeute und Zuverlässigkeit für missionskritische Anwendungen.

In Europa fördern die Entstehung neuer Einrichtungen durch GlobalFoundries und das anhaltende Wachstum von Infineon Technologies die Nachfrage nach modernsten Redundanzprüfungen. Das „Chips-Gesetz“ der Europäischen Union zielt darauf ab, die Chipproduktion in der Region bis 2030 zu verdoppeln und treibt Investitionen in ultrapures Wasser, Gase und Technologien zur Kontaminationskontrolle an, die von robusten Redundanzprüfungen abhängen, um strenge Qualitätsanforderungen zu erfüllen.

Technologielieferanten, die auf Redundanzprüfungen spezialisiert sind – wie Advantest Corporation und Teradyne – berichten von steigenden Bestellungen sowohl von etablierten Fabs als auch von neuen Akteuren in diesen Regionen. Ihre Lösungen sind zunehmend auf eine schnelle, Echtzeit-Erkennung von ultra-niedrigen Verunreinigungen und latenten Defekten ausgelegt, wobei KI-gesteuerte Analytik in den nächsten Jahren zum Standard werden soll.

Mit Blick auf die Zukunft werden sich die Schwellenmärkte in Südostasien, Indien und dem Nahen Osten voraussichtlich eigene fortschrittliche Fertigungsecosysteme entwickeln. Während diese Regionen ihre Kapazitäten erweitern, wird die Nachfrage nach ultrapuren Redundanzprüfungen zunehmen, was zu einer globalen Zusammenarbeit und der Einführung von Best-in-Class Technologien zur Gewährleistung einer konsistenten Qualität und Ausbeute angesichts der steigenden Komplexität der Chips führen wird.

Strategische Ausrichtung: Disruptive Technologien und langfristige Trends

Ultrapure Redundanzprüfungen in der Halbleiterindustrie stehen an der Spitze der Gewährleistung von Zuverlässigkeit, da sich die Gerätegeometrien weiter verkleinern und die Komplexitäten der Fertigung zunehmen. Bis 2025 wird die strategische Ausrichtung für dieses Feld stark von einer Konvergenz disruptive Technologien und eines branchenweiten Übergriffs auf null-Fehler-Herstellung geprägt sein, getrieben durch die Anforderungen von KI, Automobilen und fortschrittlichen Logikanwendungen.

Führende Halbleiterhersteller entwickeln rasch ihre Methoden zur Redundanzprüfung weiter, um höhere Standards für Reinheit und Ausbeute zu erfüllen. So hat TSMC die Verpflichtung zu fortschrittlicher Ertragssteigerung und rigoroser Defekterkennung in seinen neuesten Prozesstechnologien hervorgehoben und Integrationen von inline-Redundanzprüfungen und KI-Analytik direkt in ihre Produktionslinien vorgenommen. Ähnlich investiert Intel in Systeme zur Echtzeitvalidierung von Redundanz, die maschinelles Lernen verwenden, um latente Fehler in ihren 18A- und 20A-Fertigungsabläufen vorherzusagen und zu isolieren.

Ein bedeutender Trend im Jahr 2025 ist die Einführung fortschrittlicher Metrologie- und Inspektionswerkzeuge, die in ultrapuren Umgebungen atomare Fehler erkennen können. Applied Materials und Lam Research, zwei der weltweit führenden Anbieter von Halbleiterausrüstung, setzen Inspektionsplattformen ein, die Elektronenstrahlbilder, tiefes Lernen und redundanzbewusste Arbeitsabläufe kombinieren, um sicherzustellen, dass Prozessaberrationen schnell eingedämmt und korrigiert werden können. Diese Systeme können sub-nanometrische Verunreinigungen und elektrische Fehler erkennen und charakterisieren, die von entscheidender Bedeutung für die Validierung von Redundanzen in Speicher- und Logikchips sind.

Ein weiterer disruptiver Trend ist die Integration von Redundanzprüfungen in intelligente Fertigungsplattformen. Samsung Semiconductor testet KI-gesteuerte Redundanzüberwachung, die mit digitalen Zwillingen seiner Fabs integriert ist, um prädiktive Wartung und sofortige Prozessnachkalibrierung zu ermöglichen. Dies reduziert Ausfallzeiten und erhöht die Zuverlässigkeit der Produktion an fortschrittlichen Knoten, was direkt die Null-Fehler-Erwartungen des Automobil- und Rechenzentrumsmarktes adressiert.

Mit Blick auf die Zukunft umfasst die strategische Ausrichtung für ultrapure Redundanzprüfungen weitergehende Automatisierung und cloudbasierte Datenanalytik. Branchenkonsortien wie SEMI setzen neue Standards für die Interoperabilität von Testprotokollen und den Datenaustausch entlang der Lieferkette, um die Validierung von Redundanzen von Wafer- bis Systemebene zu rationalisieren. Wenn Fabriken zunehmend auf fortschrittliche Redundanzprüfungen angewiesen sind, erwarten Sie weitere Kooperationen zwischen Geräteherstellern, Chipmachern und Materiallieferanten, um die geschlossene Fehlerbehebung zu beschleunigen und die Grenzen der Gerätezuverlässigkeit bis 2025 und darüber hinaus zu erweitern.

Quellen & Referenzen

- imec

- Advantest Corporation

- STMicroelectronics

- Synopsys

- ASML

- Infineon Technologies

- BASF

- DuPont

- Tokyo Electron Limited

- Samsung Electronics

- Entegris

- IEEE