Tartalomjegyzék

- Vezetői összefoglaló: 2025 és a következő út

- Piacméret és növekedési előrejelzések 2030-ig

- Kulcsfontosságú hajtóerők: AI, IoT és fejlett csíkkészítés

- Ultrapuritási szabványok: Fejlődő követelmények és ipari mércék

- Legfrissebb innovációk a redundancia tesztelési módszerekben

- Legfontosabb szereplők és stratégiai szövetségek (2025-ös fókusz)

- Ellátási lánc integráció és tisztasági kihívások

- Szabályozási környezet és szabványügyi testületek (pl. SEMI.org, IEEE.org)

- Fejlődő piacok és regionális lehetőségek

- Stratégiai kilátások: Zavaró technológiák és hosszú távú trendek

- Források és hivatkozások

Vezetői összefoglaló: 2025 és a következő út

Az ultrapuris lapkák redundancia tesztelése kritikus mértékben növekszik, ahogy az ipar 2025-be lép, amit az apróbb csíkszélesség, a megbízhatóbb eszközök iránti folyamatos igény és az AI, autóipari elektronika és kvantumszámítás ilyesmi fejlett alkalmazások elterjedése hajt. Az ultrapuri környezetek elengedhetetlenek a szigorú, 5 nm alatti és következő generációs chipgyártás hozambiztosításához és megbízhatóságához. A redundancia tesztelés – ahol a biztonsági körök és a hibával szemben toleráns architektúrák rendszeresen kerülnek ellenőrzésre – kulcsszerepet játszik a termelési ellenállás biztosításában, a költséges leállások minimalizálásában és a rejtett hibák kezelésében, amelyek akár apró szennyeződés vagy folyamatvariációk miatt is felmerülhetnek.

A vezető félvezetőgyártók fokozzák a beruházásokat az ultrapuri környezetekben végzett redundancia tesztelésbe. Például a Taiwan Semiconductor Manufacturing Company (TSMC) továbbra is bővíti a redundancia valóságtalansági normáira koncentráló stratégiáit, kifejezetten a 3nm-es és 2nm-es csomópontokban. Hasonlóan, a Samsung Electronics Semiconductor kiemeli a redundancia mechanizmusok integrációját és a kifinomult teszt protokollokat legkorszerűbb gyártóhelyeiben, célja a megbízhatóság további megerősítése tekintettel a gate-all-around (GAA) tranzisztor architektúrákra.

Az eszközellátók is alkalmazkodnak ezekhez az igényekhez. Az Applied Materials és a Lam Research új struktúrákat fejlesztenek ki, amelyek az AI-alapú analitikákat használják az ultrapuri folyamatvonalak redundancia hibáinak hatékonyabb észlelésére és jellemzésére. Ezek a rendszerek a folyamat által indukált hibák figyelemmel kísérésére és a redundáns struktúrák működési integritásának érvényesítésére kerülnek bevezetésre.

Az ipari konzorciumok adatai, mint például a SEMI, azt mutatják, hogy a nemzetközi látható adatkezelés jövőbeli kiterjedése a tesztelésre és metrológiára a 7%-ot meghaladó CAGR-növekedni várható 2028-ig, tükrözve az ágazat hozambiztosításra és megbízhatóság garantálására helyezett prioritásait. Továbbá, az olyan együttműködések, mint az imec esetében felgyorsítják az új redundáns architektúrák és gyártási protokollok kifejlesztését, amelyeket a ultrapuri környezetekhez igazítanak.

A jövőre nézve, a következő néhány évben a redundancia tesztelés egyre inkább automatizált, adatközpontú és szorosan integrálódik a valós idejű folyamatellenőrzéssel. Ahogy a félvezetőgyártók a 2nm és azon túlra tolják a határokat, a nulla hibás paradigmák a redundancia tervezés, és a megszorítás elvárásain fognak nyugodni. Ez az evolúció kulcsfontosságú a jövőbeli félvezetőtechnológiák megbízhatósága, skálázhatósága és kereskedelmi érvényesülése megtartásához.

Piacméret és növekedési előrejelzések 2030-ig

A globális piac az ultrapuris lapkás redundancia tesztelés terén jelentős növekedés elé néz 2030-ig, amit a félvezető eszközök bonyolultságának növekedése, a fejlett csomópontok elterjedése (5nm, 3nm és alacsonyabb) és az ultra-megbízható chipek iránti folyamatos kereslet növel. Ahogy az eszköz geometriái zsugorodnak, és a gépesítési szint emelkedik, az abszolút tisztaság és robusztusság biztosítása a félvezető gyártási folyamatokban a redundancia tesztelést a minőségbiztosítás élvonalába helyezte.

2025-ben a vezető félvezetőgyártók, mint a Taiwan Semiconductor Manufacturing Company (TSMC), Samsung Electronics és Intel Corporation folytatják az invesztíciók bővítését az advanced redundancia tesztelési infrastruktúrába. Ezek a befektetések nemcsak a logikai és memóriacirkuláris mitikus hibák és krízisek észlelésére és enyhítésére vonatkoznak, hanem a járműipar és a küldetéstudatos ágazatok szigorodó megbízhatósági követelményeinek teljesítésére is. Például a TSMC folytatódó kapacitásbővítései és a „Zéró Hiba” kezdeményezései hangsúlyozzák az ultrapuri tesztkörnyezetek középpontját a jövőbeli terveikben.

A gyártási befektetések mellett, a tesztfelszerelés fő beszállítói, mint például az Advantest Corporation és a Teradyne, gyorsan innoválnak, hogy következő generációs automatizált tesztberendezéseket (ATE) kínáljanak, amelyek képesek támogatni a nanométeres méretű redundância tesztelési folyamatokat. Ezek a rendszerek egyre inkább AI-alapú analitikát és magas átviteli párhuzamos tesztelést használnak a lefedettség javítására és a tesztelési kilépési arány csökkentésére, megfelelve a vezető gyárak változó igényeinek.

A legfrissebb vállalati közlések és iparági ütemtervek szerint az ultrapuris lapkás redundáns tesztelési berendezések és szolgáltatások piaca várhatóan magas egyjegyű CAGR-t fog növekedni 2030-ig, az Ázsia–Csendes-óceán térségbeli kereslet vezetésével, ahogy Tajvan, Dél-Korea és Kína a legnagyobb kereslet. Ilyen új gyártóhelyek („mega fabs”) bővítése a Samsung Electronics és TSMC által 2025 és 2027 között még tovább hangsúlyozza az ágazat erős kilátásait.

Nézve a jövőt, az extrém ultraibolya (EUV) litográfia, a heterogén integráció és a chiplet architektúrák tovább növelik az ultrapuris redundancia tesztelési módszerek iránti igényt. A gyártók, felszerelésgyártók és ipari konzorciumok, mint a SEMI közötti együttműködések elősegítik a szabványok és legjobb gyakorlatok fejlődését, biztosítva, hogy a redundancia tesztelés lépést tartson a technológiai skálázással és a megbízhatósági követelményekkel 2030-ig és azon túl.

Kulcsfontosságú hajtóerők: AI, IoT és fejlett csíkkészítés

A mesterséges intelligencia (AI), az Internet of Things (IoT) és a fejlett csíkkészítési eljárások gyors fejlődése jelentősen felgyorsítja az ultrapuris lapkás redundancia tesztelés iránti keresletet. Ahogy az eszközök bonyolultsága és integrációs sűrűsége nő, különösen a 5 nm alatti csomópontoknál, a hibák elkerülésének és a megbízható működés biztosításának fontossága felértékelődik. Az AI gyorsítói például már komoly redundancia tesztelést igényelnek a járműipari, orvosi és ipari szektorokban a küldetéstudatos követelmények elérése érdekében. Az Intel Corporation és a Taiwan Semiconductor Manufacturing Company mindkét másik közleményei egyre inkább a modern redundancia sémákra és teszt protokollokra fókuszálnak a legújabb gyártási folyamatok esetében, tükrözve az iparon belüli megbízhatóság javulására tett külső erőfeszítéseket.

Az IoT elterjedése tovább növeli a redundancia tesztelési igényeket. Mivel 2025-re több milliárd összekapcsolt érzékelőt és eszközt várnak, a gyártóknak garantálniuk kell a folyamatos működést és a biztonságot, még részleges hardverhibák esetén is. Az STMicroelectronics hangsúlyozza, hogy IoT-targetált félvezetői kiterjedt redundancia és megbízhatósági szűréseken mennek keresztül, automatizált tesztelési felszereléseket használva a bonyolult hibahelyzetek szimulálására.

A chiplet architektúrák és a 3D csomagolás bevezetése is átalakítja a tesztelési módszereket. A bonyolult, több die-ból álló rendszerek nemcsak a hagyományos funkcionális teszteket, hanem a rendszer szintű redundancia ellenőrzését is megkövetelik az összekapcsolt die-k között. Az Advanced Micro Devices (AMD) új redundancia-tudatos tervezésű tesztstratégiákat fogadott el chiplet-alapú processzorai számára, míg a Synopsys és az Advantest a következő generációs tesztmegoldások bevezetésén dolgozik, amelyek e architektúrák egyedi hibamentesítési elvárásait célozzák.

- Adatok és trendek (2025 és azon túl): Az elérhető gyártók és gyártók növelik a teszt terjedelmét és a redundancia szűrési kiadásait, bejelentett 18%-os éves növekedéssel az advanced tesztfelszerelések terén (ASML). A waferek és a végső csomagolás tesztelési pontjai bővülnek, különösen az AI és a biztonságkritikus IoT alkalmazásokhoz készült chipek esetén.

- Kilátások: A következő néhány évben a félvezetőgyártók várhatóan továbbra is alkalmazzák az AI-alapú tesztmintázat-generálást és a rugalmas redundancia stratégiákat, csökkentve a tesztelési hibázásokat és javítva a mezőbeli megbízhatóságot. A valós idejű redundancia ellenőrzés integrálása a telepített eszközökbe – amelyet a szél AI és digitális ikrek segítenek – meg fogja nyomni a mezőbeli hibák és hibabeállítások észlelését és korrekcióját (Infineon Technologies).

Összefoglalva, az AI, IoT és a fejlett csíkkészítési eljárások összefonódása arra kényszeríti az ipart, hogy újradefiniálja az ultrapuris lapkás redundancia tesztelési paradigmákat, jelentős beruházásokkal és innovációkkal 2025-ig és azon túl.

Ultrapuritási szabványok: Fejlődő követelmények és ipari mércék

Az ultrapuris redundancia tesztelés alapjává válik a félvezetőgyártásban, ahogy az eszköz geometriák folyamatosan zsugorodnak és a funkcionális bonyolultság nő. A folyamatos ultrapuri víz (UPW), vegyszerek és gázok biztosításának szükségessége új szabványokat és mércéket hajtott végre a redundancia tesztelés terén az iparban. 2025-re az iparban egyre nagyobb figyelmet kap a szigorú folyamatellenőrzés, automatizálás és adatértelmezés a kiigazító követelmények fenntartása érdekében.

A vezető gyártók több rétegű redundanciát alakítanak ki ultrapuri rendszereikben a szennyezés vagy a leállás kockázatának csökkentésére. Például, az Intel jelentése szerint a wafereiket üzemeltető gyárak most kettős bemeneti UPW hurkokat, párhuzamos szűrőcsapatokat és valós idejű érzékelőket használnak, hogy automatikusan áttérjenek tartalék rendszerekre, ha észlelnek egy eltérést. E redundanciát folyamatosan stressz tesztelik szimulációkkal és élő gyakorlatokkal, hogy biztosítsák, hogy minden kritikus csomópont meg tudja tartani a félvezető szintű tisztaságot (<18 MΩ·cm a UPW esetében) még kedvezőtlen körülmények között is.

A vegyianyag-szállítók oldalán olyan cégek, mint a BASF és a DuPont együttműködnek az eszközgyártókkal, hogy érvényesítsék a redundáns szállítástechnikai és tárolási infrastruktúrát. Ezek a rendszerek időnkénti kihívás teszteken mennek keresztül, ahol a fő ellátás szándékosan meg van szüntetve, és az automatikus váltás a tartalékra sebesség és tisztaság biztosítása érdekében van ellenőrizve. A tesztadatok megosztásra kerülnek az ügyfelekkel, amely a beszállítói minőségellenőrzési auditok részét képezi és az ipari standardoknak, mint például a SEMI F63 és az ITRS útmutatók, megfelel (SEMI).

A következő néhány év kilátása a mércék szigorítására mutat. A SEMI szervezet aktívan felülvizsgálja a redundancia érvényesítésére vonatkozó szabványait, hangsúlyozva a digitális nyomon követhetőséget, az eseménynaplózást és a prediktív hibaanalitikát. A felszerelés beszállítók, mint az Evoqua Water Technologies most integrált tesztcsomagokat kínálnak, amelyek a fizikai váltásos teszteket ötvözik a felhőalapú diagnosztikával a folyamatos ellenőrzés biztosítása érdekében.

A 2 nm alatti technológiák felé való elmozdulás várhatóan még szigorúbb redundancia tesztelési protokollokat fog hozni. A gyártók és a beszállítók közötti valós idejű adatmegosztás, amint azt a TSMC legutóbbi kezdeményezései is tanúsítják, egyre nagyobb normává válik. Ez az együttműködő megközelítés nemcsak fokozza az ellenállást, hanem gyors válaszadást is biztosít az anomáliákra, új ipari mércéket állítva fel a megbízhatóság és a folyamat integritása szempontjából egy olyan környezetben, ahol minden hiányosság millió dolláros következményekkel járhat.

Legfrissebb innovációk a redundancia tesztelési módszerekben

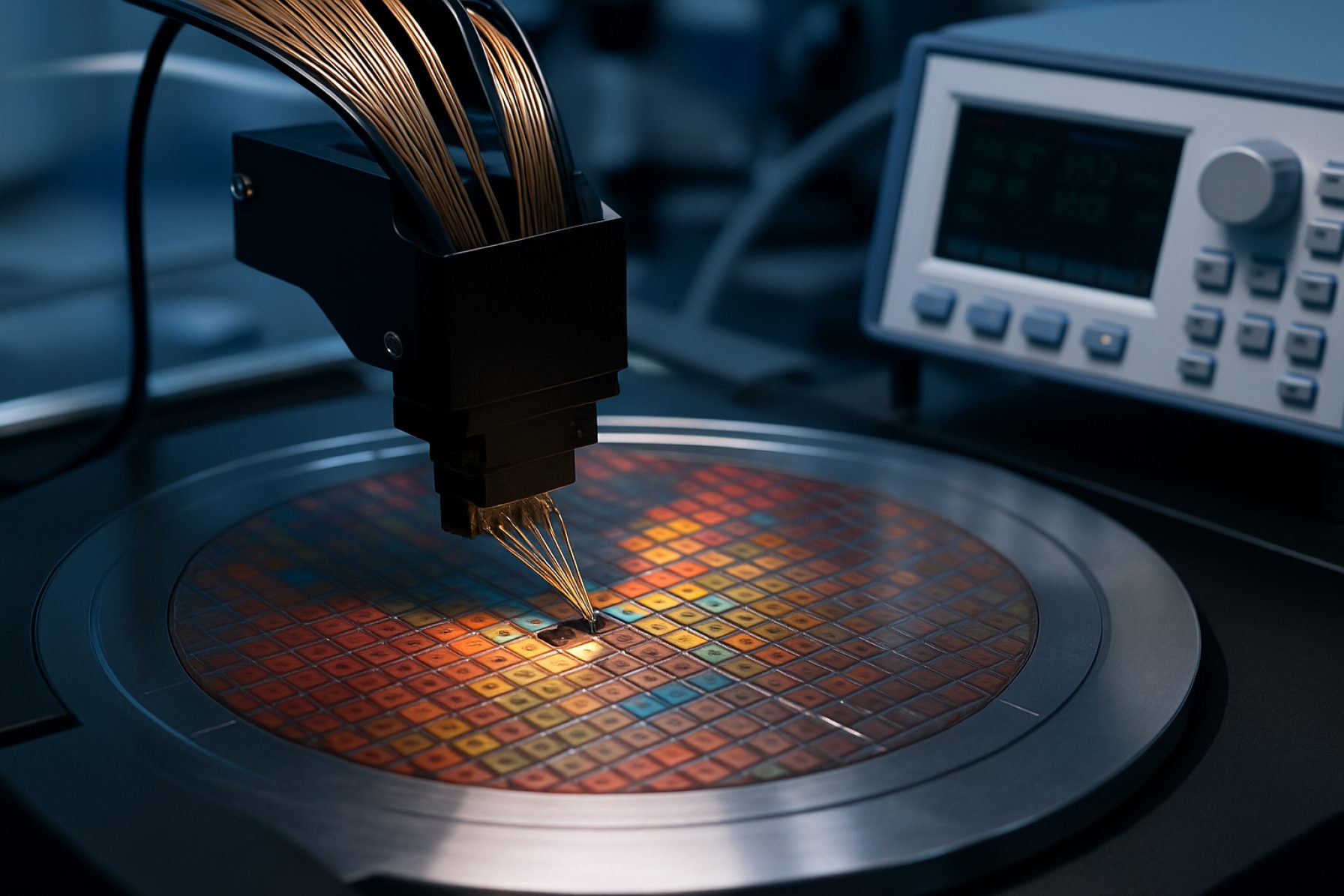

Az ultrapuris félvezetőgyártás folyamatosan a készülékek teljesítményének határait feszegeti, a redundancia tesztelési módszerek pedig gyorsan fejlődnek, hogy biztosítsák a megbízhatóságot a egyre bonyolultabb integrált áramkörök (IC-k) esetében. Ahogy az eszközgeometriák zsugorodnak és az ultra-magas hozambiztosítási igények fokozódnak, a redundancia tesztelés – különösen a memória tömbök és logika esetében – az innováció fókuszává vált.

2025-re a vezető félvezetőgyártók képesek komoly redundancia-elemzési és javítási megoldásokat telepíteni a tesztfolyamatukba. Például a Taiwan Semiconductor Manufacturing Company (TSMC) kihangsúlyozta az adaptív redundancias algoritmusok alkalmazását a 3nm és 2nm gyártási folyamatokban, a folyamat adatokat és a gépi tanulást felhasználva a dinamikus hibahelyzetek lokalizálására és a tartalék cellák allokációjára. Ez a megközelítés csökkenti a túlzott és alacsony mértékből adódó problémákat, növelve mind a hozamot, mind a hosszú távú megbízhatóságot.

A memóriatermékek esetében a Samsung Electronics valós idejű redundanciát értékel a legkorszerűbb DRAM és NAND flash vonalain. Az élenjáró beépített önjavító (BISR) áramkörök, amelyeket prediktív analitikával meglovagoltak, lehetővé teszik a hibás cellák gyorsazzon és cserét a wafersor során, még akkor is, ha a tömbök méretei megülik a több száz gigabitet. Ezek az innovációk minimalizálják a késleltetett hibák kockázatát a telepítés után, és optimalizálják a chipen lévő redundáns elemek kihasználását.

Az automatizált tesztberendezések (ATE) gyártói, mint az Advantest Corporation, új platformokat vezetnek be, amelyek natív támogatást nyújtanak a redundancia-tudatos teszt protokollok számára. A 2024-ben indított V93000 sorozat lehetővé teszi a párhuzamos tesztelést és in-situ javítást a több die-ból álló csomagok és chipletek esetében – kulcsfontosságú jellemzőként ismerik el, ahogy az előremutató csomagolás egyre bővül a magas teljesítményű számítástechnikai és mesterséges intelligencia alkalmazások terén.

A félvezető-felszerelési ökoszisztéma szintén reagál a tiszta tesztkörnyezetek iránti igényre. A Lam Research 2025-re kontaminálásmentes waferkezelés és feldolgozókamrák terén elért előrehaladásokról számolt be, ami közvetlenül támogatja a redundancia tesztelések épségét a korszerű csomópontoknál, ahol még az atom szintű szennyeződések is torzíthatják a hozamilag adatokat vagy elrejthetik a késlekedő redundancia hibákat.

A jövőbe nézve a végeszeti analitika, a hardver-szoftware koordinált optimalizálása és a szigorúbb menetellenőrzés fokozni fogja a redundancia tesztelést. A digitális ikrek integrációja és AI-alapú hiba-előrejelzés is közeleg, ígéretes megoldásokat kínálva a null hibás gyártás érdekében, ahogy az eszközök bonyolultsága nő. A gyárak, az eszközgyártók és a chipgyártók közötti együttműködés elengedhetetlen azért, hogy ezeket az előrehaladásokat megvalósíthassák, és biztosítsák az ultrapuri, ultra-megbízható félvezetők ellátását.

Legfontosabb szereplők és stratégiai szövetségek (2025-ös fókusz)

2025-re az ultrapuris lapkás redundancia tesztelés területe jelentős tevékenységet mutat a legfontosabb ipari szereplők, stratégiai partnerségek és az advanced tesztelt megoldásokba történő befektetések között. Ahogy a félvezetők gyártási csomópontjai folyamatosan csökkennek, a ultrapuri környezetek és a robusztus redundancia tesztelés iránti igény fokozódik. A kulcsszereplők – beleértve a felszerelésgyártókat, a félvezető gyártókat és az anyagbeszállítókat – egyre inkább együttműködnek az észlelés szigorúbb követelményeinek és a folyamat megbízhatóságának kezelésére.

- Applied Materials, Inc. élvonalban marad, előrehaladott vizsgálati és metrológiás platformokat biztosítva, amelyek lehetővé teszik a nanométeres skálájú redundancia tesztelést. 2025-ben a cég bejelentette a legfontosabb logikai és memóriaggyártókkal való együttműködési lehetőségek bővítését a redundancia tesztelő modulok co-fejlesztése érdekében, amelyeket ultrapuri környezetekhez optimalizáltak (Applied Materials, Inc.).

- ASML Holding NV továbbra is fontos szereplő marad, különösen az EUV litográfiai rendszerein keresztül, amelyek szigorú in-line redundancia tesztelést igényelnek a működési stabilitás biztosításához. 2025 elején az ASML bővítette a vezető chipgyártókkal való szövetségét, hogy integrálja a saját redundancia tesztelési rutinját az EUV szerszámokba, célja a szennyeződések minimalizálása és a tervezett leállások elkerülésére (ASML Holding NV).

- Tokyo Electron Limited (TEL) elmélyítette partnerei kapcsolatát globális gyárakkal és gyártókkal, a ultrapuri folyamat modulok és a redundanciák ellenőrzésére összpontosítva. A TEL 2025-ös kezdeményezései közé tartozik a legfontosabb gyárakkal közösen szervezett kísérleti programok, a kritikus hozambiztonság érdekében végzett automatizált teszt algoritmusok finomítása (Tokyo Electron Limited).

- Samsung Electronics és TSMC – mint a világ legnagyobb félvezetőgyártói – mindketten fektettek be a belső redundancia tesztelési innovációkba. 2025-ben a Samsung bejelentette egy AI-айrü mгоndelmi platform implementálását fejlett logikai vonalain, míg a TSMC kiterjesztette több szolgáltató redundancia minőségi programját, hogy új teszt protokollokat vonjon be a 2 nm-es gyártás esetében (Samsung Electronics; TSMC).

- Ipari szövetségek, mint például a SEMI koordinálásában, tovább mozdították elő a tesztelési normák és legjobb gyakorlatok harmonizálódását, a az új munkacsoportok 2025-ben kifejezetten az ultrapuri gyártási környezetben végzett redundancia érvényesítésre összpontosítanak (SEMI).

A jövőt nézve, a szektor várhatóan továbbra is tapasztalni fogja a felszerelésgyártók és az eszközgyártók közötti konvergenciát, a stratégiai szövetségek pedig egyre inkább az egyéni, in-line redundancia tesztmegoldások co-fejlesztésére fognak összpontosítani. Ez az együttműködő megközelítés valószínű, hogy alátámasztja a következő innovációs hullámot az ultrapuri félvezetőgyártásban, biztosítva a magasabb hozamot és a megerősített eszköz megbízhatóságot 2026-ig és azon túl.

Ellátási lánc integráció és tisztasági kihívások

Az ultrapuris lapkás redundancia tesztelés a félvezető ipar integrációjának kulcsfontosságú aspektusává válik, mivel a félvezető ipar egyre szigorúbb tisztasági követelményekkel és a gyártási folyamatok növekvő bonyolultságával néz szembe. Ahogy a chipek geometrái zsugorodnak és az eszközök érzékenyebbé válnak a szennyeződésekre, a megbízhatóság és a tisztaság biztosítása mind a nyersanyagok, mind a késztermékek esetén a redundancia tesztelés révén egyike lett a technikai és logisztikai kihívásoknak.

2025-re a figyelem a fejlett redundancia tesztelési protokollok integrálására irányul az ellátási láncban. A legnagyobb öntödék és anyagszállítók mostantól előírják az ultrapuri gázok, vegyszerek és szilícium lapkák többlépcsős tesztelését különböző feldolgozási csomópontokon az észlelt szennyeződésekből adódó hibakockázat minimalizálása érdekében. Például az Intel Corporation stratégiákat vázolt az eljárás vegyszereinek redundáns inline és végponti tesztelésére, hogy biztosítsa, hogy bármelyik ponton bekövetkezett meghibásodást vagy szennyeződést gyorsan észlelnek és elkülönítenek, mielőtt a széleskörű gyártási hozamokra hatással lennének.

Egy másik fontos fejlemény az ipari testületek, mint például a SEMI, által bevezetett standardizált tisztasági mutatók és tesztelési módszerek közötti együttműködési buktatások. 2024 és 2025 folyamán a SEMI Nemzetközi Szabványprogramja dolgozott a chipgyártókkal, eszközzárósokkal és vegyi árujakkal a vegyianyag-batchok redundáns tisztasági érvényesítésének protokolljainak finomhangolásán, beleértve a kémiai tétel duális forrás-verifikációját és gázáramok valós idejű ellenőrzését. Az ilyen kezdeményezések közvetlenül célozzák az ellátási lánc integrációját, egységes elvárások és adatmegosztás követelmények ösztönzésével a beszállítók és gyártók között.

A vezető anyagbeszállítók, mint az Entegris és a DuPont fejlett érzékelőhálózatokat és automatizált analitikát igényelnek a folyamatos, redundáns tisztasági ellenőrzések lehetővé tételéhez. Ezek a rendszerek képesek nyomon követni a szennyeződéseket a trillió részecskék szintjéig, és olyan hatékony adatokat kínálnak, amelyeket az integrált minőségönellenőrzési keret részeként a leárás partnerekkel megosztanak. Ez különösen fontos, mivel az ipar a 2nm alatti gyártási technológiák feléé kacsázik, ahol még a nyomokban lévő szennyezők is veszélyeztethetik az eszközök integritását.

A következő néhány évben a redundancia tesztelés várhatóan nemcsak automatizáltabb, hanem mélyebben beépített részekké is válik a digitális ellátási lánc irányítási rendszereibe. A vállalatok blokklánc-alapú nyomon követési megoldásokat és biztonságos adatmegosztás platformját fejlesztenek egyaránt, hogy nyomon követhessék és érvényesíthessék minden tisztasági tesztet az ellátási lánc mentén, ahogy azt a TSMC és ökoszisztéma partnerei is bemutatták. Ez a digitalizáció segít azonosítani a potenciális megszakításokat vagy hiányosságokat a redundanciában, mielőtt hatással lehetnek a nagy volumenű gyártásra, ezáltal tovább védik az előremutató félvezetők tisztaságát és megbízhatóságát.

Szabályozási környezet és szabványügyi testületek (pl. SEMI.org, IEEE.org)

Az ultrapuris lapkás redundancia tesztelés szabályozási környezete gyorsan változik, ahogy az ipar technológiai előrelépéseket és egyre növekvő megbízhatósági követelményeket ütközik. Az ultrapuri környezetek kritikus fontosságúak a félvezető gyártáshoz, mivel a legkisebb szennyeződések meghiúsíthatják a wafe sikerét vagy rejtett hibákat okozhatnak az eszközökben. A redundancia tesztelés – a több tesztelési módszer vagy tartalék rendszerek alkalmazása – fókuszba került, hogy biztosítsa, hogy a tesztelési folyamatok elég robusztusak legyenek a lehetséges hibák észlelésére és mérséklésére.

A kulcsszabvány-fejlesztő szervezetek, mint például a SEMI és az IEEE, alapvető szerepet játszanak a redundáns tesztelés szabályozási környezetének formálásában. A SEMI F63 szabvány például a félvezetőgyártás ultrapuris vizeinek (UPW) minőségére vonatkozó iránymutatásokat tartalmaz, közvetve hatással van a redundancia szabályaira azáltal, hogy meghatározza a szennyeződés kockázati határokat és monitorozási követelményeket. 2025-ben a SEMI folytatja a szabványok frissítését az UPW és gázrendszerek tesztelésére és észlelésére vonatkozóan, amelyek a kritikus folyamatlépések redundanciastratégiáira elengedhetetlenek.

Hasonlóképpen az IEEE folyamatban lévő kezdeményezései relevánsak a tesztmódszer ismételhetőségére, a rendszerhibák toleranciájára és a félvezető eszközök minősítésére vonatkozóan. IEEE 1687 (IJTAG) és a kapcsolódó szabványok keretet nyújtanak az időben történő redundancia és hibaérzékelésre érvényes berendezésekhez. Ahogy az eszközök bonyolultabbá válnak és a gyártási csomópontok zsugorodnak, a teszt-standardok fokozatosan hangsúlyozzák a redundanciát, nemcsak a tesztelési rutinokban, hanem a chipben beépített önellenőrzési (BIST) architektúrákban is.

Az elmúlt években a globális szabályozó testületek és ipari konzorciumok hangsúlyozták a legjobb gyakorlatok harmonizálásának fontosságát. A SEMI Nemzetközi Szabványprogramja például elősegíti az egyesült határokon történő nyomon követését előírásaival és a redundancia érvényesítésével kapcsolatosan, tükrözve a félvezető-ellátási láncok globális jellegét. 2025-ben a SEMI műszaki bizottságai azzal a céllal működnek együtt a regionális hatóságokkal, hogy a redundancia tesztelési protokollok megfeleljenek a helyi szabályozásoknak és nemzetközi normáknak.

A következő néhány évre nézve a szabályozási környezet várhatóan további szigorodásra számíthat. Az olyan magas megbízhatóságú alkalmazások elterjedésével – mint az autóipar, légi- és egészségügyi elektronika – valószínű, hogy a hatóságok szigorúbb redundanciát fognak elvárni, és dokumentációt kérnek. Standardizáló testületek, mint a SEMI és az IEEE, új iránymutatásokat várhatóan a fejlett redundancia érvényesítési módszerekre vonatkozóan fognak kiadni, egyre növekvő követelményekkel a digitális nyomon követhetőség, a prediktív analitika és az AI-alapú tesztfigyelés terén. Az ipar minden szereplőjének rugalmasnak kell maradnia, proaktívan alkalmazkodnia a változó szabványokhoz annak érdekében, hogy fenntartják a megfelelést és a versenyelőnyt.

Fejlődő piacok és regionális lehetőségek

Az ultrapuris lapkás redundancia tesztelés tája 2025-ben gyorsan fejlődik, amelyet a globális fejlett chipgyártás bővítése és az integrált áramkörök növekvő bonyolultsága formál. Ahogy a vezető öntödék jövőőr gazdálkodási irányelvük mellett fejlesztik ki az új generációs csomópontokat – például a 3nm és az alatti csomópontokat –, a szigorú redundancia tesztelési protokollok iránti igény robbanásszerűen nő, különösen az újonnan fejlődő félvezetőgyártási központokban.

2025-re jelentős növekedés tapasztalható az ázsiai–csendes-óceáni térségben, Tajvan, Dél-Korea és Kína vezető szerepet játszik az új gyártási kapacitásokba történő befektetésekben. A Taiwan Semiconductor Manufacturing Company (TSMC) és a Samsung Electronics bővítik fejlett gyártási képességeiket, hangsúlyozva a szennyeződések minimalizálásának és kritikus folyamatlépések redundanciájának biztosítását. Ezek a cégek integrálják az avanzsred redundancia tesztelést, hogy megfelelhessenek az egyre szigorodó hibásodási kockázati és megbízhatósági normáknak, különösen az autóipari és AI-orientált chipek esetében.

Eközben az Egyesült Államok visszatér a félvezetőgyártás iránti elköteleződéshez, amit a szövetségi ösztönzők és a helyi beszállítókkal való partnerség segít. Az Intel aktívan új gyártókat épít Arizona és Ohio államokban, felszerelt rendszerekkel az ultrapuri folyamatok tesztelésére. Ezek a rendszerek inline hibaellenőrzést és valós idejű analitikát alkalmaznak a potenciálisan gyenge pontok gyors érzékelésére és mérséklésére, ezáltal javítva a hőszigetelést és megbízhatóságát a küldetési kritikus alkalmazások számára.

Európában a GlobalFoundries új létesítményeinek megjelenése és a Infineon Technologies folyamatos növekedése a határvonalakhoz képest keresletet generál az élvonalbeli redundancia tesztelés iránt. Az Európai Unió „Chips Act” célja, hogy megduplázza a régió csipgyártását 2030-ra, amely további befektetéseket ösztönöz az ultrapuri vízben, gázokban és szennyezésellenőrző technológiákban, amelyek megbízható redundancia tesztelésen alapulnak a szigorú minőségi követelmények teljesítésére.

A redundanciás teszteléssel foglalkozó technológiai beszállítók – mint például az Advantest Corporation és a Teradyne – fokozódó megrendeléseket tapasztalnak az előrehaladó gyáraktól és új belépőktől ezekben a régiókban. Megoldásaik egyre inkább a rendkívül mozgékony, valós idejű ultrahangokat és hibamentesség és rejtett hibák előtt hoznak létre, az AI-alapú analitikát várva az elkövetkező években.

Nézve a jövőt, a fejlődő piacok Délkelet-Ázsiában, Indiában és a Közel-Keleten saját fejlett gyártási ökoszisztémáik kifejlesztésére kötelezik el magukat. Ahogy ezek a régiók növelik a kapacitást, az ultrapuris redundancia tesztelés iránti demand meg fog nőni, globális együttműködést ösztönözve és a legjobb szolgáltatások elfogadása érdekében a kontinens rengeteg minősége és hozama érdekében az emelkedő chip bonyolultsága mellett.

Stratégiai kilátások: Zavaró technológiák és hosszú távú trendek

Az ultrapuris lapkás redundancia tesztelés első vonalában áll a megbízhatóság biztosítása érdekében, ahogy a készülék geometriai értéke folyamatosan csökkenthető és a gyár bonyolultabbá válik. 2025-re a szakterület stratégiai átláthatósága erősen alakítja a zavaró technológiák és az ipari ösztönzés felé való elmozdulás globális zökkenésének azt a szükségességét, amely elengedhetetlenné teszi a nulla hibás gyártást, mivel az AI, a járműipar és a fejlett logika alkalmazásainak igényeit ülteti el.

A vezető félvezetőgyártók gyorsan fejlődnek a redundancia tesztelési módszereikének terén, hogy megfeleljenek a tisztasági és hozambiztonsági normáknak. Például a TSMC kiemelte elkötelezettségét az értékbecslés javítása és a szigorú hibafelfedezés érdekében a legújabb gyártási technológiák esetében, integrálva az inline redundancia tesztelést és az AI-alapú analitikát közvetlenül a termelési vonalaikba. Hasonlóképpen, az Intel valós idejű redundáns érvényesítési rendszerekbe fektet be, gépi tanulás révén az elrejtett hibák előrejelzésére és a 18A és 20A gyártási folyamatai újra elemzésére.

A 2025-ös jelentős trend az előrehaladott metrológiai és ellenőrzési módszerek bevezetése, amelyek képesek érzékelni az atom véres területek szennyeződését az ultrapuri környezetekben. Az Applied Materials és a Lam Research, a világ vezető félvezetőberendezés gyártóinál, indítanak be olyan népszerű és innovatív eljárásokat, amelyek az élő orientálási, előrehaladást, mély tanulás támogatásával a redundancia tesztelés folyamatainak megsegítésére, a lehető legszélesebb skálák ellenőrzésére törekedve. Ezek a rendszerek képesek és jellemzik a szub-nanométer szennyeződéseket és elektormos hibákat, amelyek kulcsfontosságúak a memória és logikai chipek redundancia érvényesítéséhez.

Egy másik zavaró trend a redundancia tesztelés integrálása intelligens gyártási platformokba. A Samsung Semiconductor a pilótákban az AI-alapú redundancia figyelmi mintákat integrál, digitális ikrekkel, amelyek lehetővé teszik a prediktív karbantartást és a folyamat azonnali újbóli kalibrálását. Ez csökkenti a leállásokat és növeli a fejlett csomópontgyártás megbízhatóságát, közvetlenül válaszolva az autóipari és adatközpontra vonatkozó nulla hibás elvárásaira.

Nézve a jövőt, az ultrapuris lapkás redundancia tesztelési stratégiákhoz további automatizáció és felhőalapú adatanalitika bevezetése is elvárt. Az ipari konzorciumok, mint a SEMI új szabványokat állítanak fel a tesztelési protokollok interoperabilitására és az adatok megosztása az ellátási lánc mentén, hogy a redundancia ellenőrzését leegyszerűsítse a wafertől a rendszer szintig. Ahogy a gyárak egyre inkább támaszkodnak a fejlett redundancia tesztelésre, várható, hogy továbbra is együttműködnek az eszközkészítőkkel, chipgyártókkal és anyagszállítókkal, hogy felgyorsítsák a zártkörű hiba elhárítást és megnyújtsák a készülékek megbízhatóságát 2025-ig és azon túl.

Források és hivatkozások

- imec

- Advantest Corporation

- STMicroelectronics

- Synopsys

- ASML

- Infineon Technologies

- BASF

- DuPont

- Tokyo Electron Limited

- Samsung Electronics

- Entegris

- IEEE