Stablo s sadržajem

- Izvršno sažetak: 2025. i put unaprijed

- Veličina tržišta i prognoze rasta do 2030.

- Ključni pokretači: AI, IoT i napredna proizvodnja čipova

- Ultrapuri standardi: Evolucijski zahtjevi i industrijski standardi

- Najnovije inovacije u metodama testiranja redundancije

- Glavni igrači i strateški savezi (fokus na 2025.)

- Integracija lanaca opskrbe i izazovi čistoće

- Regulatorno okruženje i tijela za standarde (npr. SEMI.org, IEEE.org)

- Emergenta tržišta i regionalne prilike

- Strateški pregled: Disruptivne tehnologije i long-term trendovi

- Izvori i reference

Izvršno sažetak: 2025. i put unaprijed

Ultrapuri testovi redundancije u poluvodičkoj industriji dobivaju na važnosti ulaskom u 2025. godinu, potaknuti neumornim zahtjevima za manjim čipovima, većom pouzdanošću uređaja i proliferacijom naprednih aplikacija kao što su AI, automobilska elektronika i kvantno računarstvo. Ultrapuri uvjeti su ključni za postizanje strogo definiranih zahtjeva za prinos i pouzdanost u proizvodnji čipova ispod 5 nm i sljedeće generacije. Testiranje redundancije – gdje se sustavno provjeravaju rezervni krugovi i arhitekture otporne na greške – postalo je ključ za osiguravanje otpornosti proizvodnje, smanjenje skupih zastoja i rješavanje latentnih nedostataka koji se mogu pojaviti čak i zbog malih nečistoća ili varijacija u procesu.

Vodeći proizvođači poluvodiča povećavaju ulaganja u testiranje redundancije unutar ultrapurih okruženja. Na primjer, Taiwan Semiconductor Manufacturing Company (TSMC) nastavlja proširivati svoj fokus na validaciju redundancije kao dio svojih strategija kontrole procesa i upravljanja nedostacima, posebno u svojim 3nm i 2nm čipovima. Slično tome, Samsung Electronics Semiconductor ističe integraciju mehanizama redundancije i sofisticiranih testnih protokola u svojim suvremenim tvornicama, s ciljem daljnjeg jačanja pouzdanosti uređaja dok se smanjuje na transistor arhitekture s potpunim obuhvatom (GAA).

Dobavljači opreme se također prilagođavaju ovim zahtjevima. Applied Materials i Lam Research inoviraju alate za inspekciju wafers i metrologiju koji koriste analitiku vođenu AI za efikasnije otkrivanje i karakterizaciju nedostataka redundancije u ultrapurim procesnim linijama. Ovi sustavi se koriste za praćenje nedostataka uzrokovanih procesom i za validaciju operativne integriteta redundatnih struktura.

Podaci iz industrijskih konzorcija, kao što je SEMI, ukazuju da će ulaganja u testiranje i metrologiju za napredne sheme redundancije rasti po CAGR-u većem od 7% do 2028. godine, što odražava prioritet sektora na upravljanju prinosom i osiguranju pouzdanosti. Nadalje, suradnički napori poput onih u imec ubrzavaju razvoj novih arhitektura redundancije i proizvodnih protokola prilagođenih ultrapurim okruženjima.

Gledajući unaprijed, sljedećih nekoliko godina vidjet će da testiranje redundancije postane sve automatiziranije, usmjereno na podatke i čvrsto integrirano s kontrolom procesa u stvarnom vremenu. Kako proizvođači poluvodiča teže 2nm i dalje, paradigme bez nedostataka će ovisiti o napretku u dizajnu i testiranju redundancije unutar ultrapurih okruženja. Ova evolucija će biti ključna za održavanje pouzdanosti, skalabilnosti i komercijalne održivosti budućih tehnologija poluvodiča.

Veličina tržišta i prognoze rasta do 2030.

Globalno tržište ultrapurih testova redundancije poluvodiča spremno je za značajan rast do 2030. godine, potaknuto rastućom složenošću poluvodičkih uređaja, proliferacijom naprednih čipova (5nm, 3nm i manje) i rastućom potražnjom za ultra-pouzdanim čipovima u kritičnim aplikacijama kao što su automobili, podatkovni centri i AI. Kako se geometrija uređaja smanjuje i razina integracije raste, potreba za osiguravanjem apsolutne čistoće i robusnosti u procesima proizvodnje poluvodiča stavlja testiranje redundancije u središte osiguranja kvalitete.

U 2025. godini, vodeći proizvođači poluvodiča kao što su Taiwan Semiconductor Manufacturing Company (TSMC), Samsung Electronics i Intel Corporation nastavljaju povećavati svoja ulaganja u infrastrukturu za napredno testiranje redundancije. Ova ulaganja su usmjerena ne samo na otkrivanje i ublažavanje latentnih nedostataka u logici i memorijskim krugovima već i na zadovoljavanje sve strožih zahtjeva pouzdanosti koje zahtijevaju automobilski i kritični sektori. Na primjer, kontinuirana proširenja kapaciteta TSMC-a i njihov fokus na inicijative “Zero Defect” naglašavaju središnju ulogu ultrapurih testnih okruženja u njihovom planu.

Paralelno s ulaganjima u tvornice, veliki dobavljači opreme za testiranje poput Advantest Corporation i Teradyne, Inc. brzo inoviraju kako bi pružili rješenja za automatizirano testiranje (ATE) sljedeće generacije sposobna podržati testiranje redundancije na procesnim čipovima u nanometarskom rasponu. Ovi sustavi sve više koriste analitiku vođenu AI i testiranje u velikim serijama kako bi poboljšali pokrivenost i smanjili stope testnih promašaja, zadovoljavajući razvijajuće potrebe vrhunskih tvornica.

Prema nedavnim korporativnim objavama i industrijskim planovima, tržište opreme i usluga ultrapurih testova redundancije u poluvodičima očekuje se da će rasti po složenoj godišnjoj stopi (CAGR) u višim jednoznamenkastim brojkama do 2030. godine, pri čemu će regija Azija-Pacifik – s dominacijom Tajvana, Južne Koreje i Kine – ostati glavni motor potražnje. Proširenje novih proizvodnih objekata (“mega fab”) od strane Samsung Electronics i TSMC u razdoblju 2025.-2027. dodatno podcrtava robusnu perspektivu sektora.

Gledajući unaprijed, usvajanje ekstremne ultraljubičaste (EUV) litografije, heterogene integracije i arhitektura čipleta dodatno će povećati oslanjanje na metode testiranja ultrapurih redundancija. Suradnički napori između proizvođača, dobavljača opreme i industrijskih konzorcija kao što je SEMI očekuje se da će ubrzati razvoj standarda i najboljih praksi, osiguravajući da testiranje redundancije prati tehnološko povećanje i zahtjeve pouzdanosti do 2030. godine i dalje.

Ključni pokretači: AI, IoT i napredna proizvodnja čipova

Brza evolucija umjetne inteligencije (AI), Interneta stvari (IoT) i napredne proizvodnje čipova značajno ubrzava potražnju za ultrapurim testovima redundancije poluvodiča. Kako složenost uređaja i gustoća integracije raste, posebno kod čipova ispod 5 nm, osiguranje otpornosti na greške i pouzdane operacije postaje od suštinskog značaja. Na primjer, AI akceleratori sada zahtijevaju robusno testiranje redundancije kako bi postigli niske stope nedostataka potrebne za kritične aplikacije u automobilskoj, medicinskoj i industrijskoj sferi. Intel Corporation i Taiwan Semiconductor Manufacturing Company izvještavaju o rastućem fokusu na napredne sheme redundancije i protokole testiranja za svoje najnovije procesne čipove, odražavajući promjenu u industriji prema poboljšanoj pouzdanosti.

Proliferacija IoT dodatno pojačava potrebe za testiranjem redundancije. S milijardama međusobno povezanih senzora i uređaja koji se očekuju do 2025. godine, proizvođači moraju osigurati kontinuiranu dostupnost i sigurnost, čak i u prisustvu djelomičnih hardverskih neuspjeha. STMicroelectronics ističe da njezini poluvodiči namijenjeni IoT-u prolaze kroz produženo testiranje redundancije i pouzdanosti, koristeći automatizirane testne opreme sposobne simulirati složene načine grešaka.

Uvođenje arhitektura čipleta i 3D pakiranja na naprednim čipovima također transformira testne metodologije. Složeni višeslojni sustavi zahtijevaju ne samo tradicionalne funkcionalne testove, već i verifikaciju redundancije na razini sustava između međusobno povezanih čipova. Advanced Micro Devices (AMD) usvojio je nove strategije dizajniranja za testiranje (DFT) usmjerene na redundanciju za svoje čiplete, dok Synopsys i Advantest uvode rješenja za testiranje sljedeće generacije kako bi zadovoljili jedinstvene zahtjeve za otpornost na greške ovih arhitektura.

- Podaci i trendovi (2025. i dalje): Tvrtke bez tvornica i tvornice povećavaju svoj proračun za pokrivenost testovima i testiranje redundancije, s izviješćenom stopom rasta od 18% na godišnjoj razini za potrošnju na naprednu testnu opremu (ASML). Točke umetanja za testiranje wafers i konačnih paketa se šire, posebno za čipove namijenjene AI i sigurnosno kritičnim IoT aplikacijama.

- Perspektiva: U sljedećih nekoliko godina, očekuje se da će proizvođači poluvodiča dodatno prihvatiti generiranje testnih obrazaca vođenih AI i adaptivnim strategijama redundancije, smanjujući promašaje testiranja i poboljšavajući pouzdanost na terenu. Integracija praćenja redundancije u stvarnom vremenu u implementiranim uređajima – omogućena kroz edge AI i digitalne blizance – će pomaknuti granice otkrivanja i ispravljanja grešaka na terenu (Infineon Technologies).

U sažetku, konvergencija AI, IoT i napredne proizvodnje čipova prisiljava industriju da redefinira paradigme testiranja redundancije u ultrapurim poluvodičima, s značajnim ulaganjima i inovacijama koje se prognoziraju do 2025. i dalje.

Ultrapuri standardi: Evolucijski zahtjevi i industrijski standardi

Testiranje redundancije u ultrapurim uvjetima postaje kamen temeljac proizvodnje poluvodiča kako se geometrija uređaja nastavlja smanjivati i funkcionalna složenost raste. Potreba za osiguranjem neprekidne opskrbe ultrapurinom vodom (UPW), kemikalijama i plinovima potaknula je nove standarde i mjerila za testiranje redundancije širom industrije. U 2025. godini, sektor svjedoči konvergenciji strogog upravljanja procesima, automatizacije i analitike podataka kako bi se održali ovi zahtjevi.

Vodeći proizvođači implementiraju višeslojne redundancije u svojim ultrapurim sustavima kako bi umanjili rizik od kontaminacije ili zastoja. Na primjer, Intel izvještava da njegove tvornice za wafers sada koriste dual-feed UPW petlje, paralelne filtražne linije i senzore u stvarnom vremenu za automatsko prebacivanje na rezervne sustave ako se otkrije odstupanje. Ova redundancija kontinuirano se testira kroz simulacije i stvarne vježbe, osiguravajući da svi kritični čvorovi mogu održati čistoću pogodne za poluvodiče (<18 MΩ·cm za UPW) čak i u nepovoljnim scenarijima.

S druge strane, u opskrbi kemikalijama, tvrtke kao što su BASF i DuPont surađuju s proizvođačima uređaja kako bi validirali redundantnu infrastrukturu dostave i skladištenja. Ovi sustavi prolaze kroz периодično testiranje izazova, gdje se primarna opskrba namjerno prekida i automatsko prebacivanje na rezervnu opskrbu se prati u pogledu brzine i osiguranja čistoće. Podaci iz ovih testova dijele se s kupcima, čineći dio revizija kvalitete dobavljača i usklađenosti s industrijskim standardima kao što su SEMI F63 i ITRS smjernice (SEMI).

Perspektiva za sljedeće nekoliko godina ukazuje na daljnje pooštravanje standarda. Organizacija SEMI aktivno revidira svoje standarde za validaciju redundancije, naglašavajući digitalnu tragovnost, evidenciju događaja i analitiku prediktivnog neuspjeha. Dobavljači opreme kao što je Evoqua Water Technologies sada nude integrirane testne pakete, kombinirajući fizičke testove prebacivanja s analitikom u oblaku za kontinuiranu verifikaciju.

Pritisak prema tehnologijama procesa ispod 2 nm očekuje se da će dodatno potaknuti strože protokole za testiranje redundancije. Razmjena podataka u stvarnom vremenu između proizvođača i dobavljača, kako pokazuje nedavna inicijativa TSMC-a, postaje standardna praksa. Ovaj suradnički pristup ne samo da povećava otpornost, već i osigurava brzu reakciju na anomalije, postavljajući nove industrijske standarde za pouzdanost i integritet procesa u okruženju u kojem bilo kakva propust može imati višemilijunske posljedice.

Najnovije inovacije u metodama testiranja redundancije

Proizvodnja ultrapurih poluvodiča nastavlja pomjerati granice performansi uređaja, a metodologije testiranja redundancije brzo se razvijaju kako bi osigurale pouzdanost u sve složenijim integriranim krugovima (IC). Kako se geometrija uređaja smanjuje i zahtjevi za ultra-visokim prinosom povećavaju, testiranje redundancije – posebno za memorijske nizove i logiku – postalo je fokus inovacija.

U 2025. godini vodeći proizvođači poluvodiča implementiraju napredna rješenja za analizu redundancije i popravak integrirana unutar svojih testnih tokova. Na primjer, Taiwan Semiconductor Manufacturing Company (TSMC) istaknula je upotrebu adaptivnih algoritama redundancije u svojim 3nm i 2nm procesnim istočnicama, koristeći podatke iz testiranja na licu mjesta i inteligenciju stroja za dinamičku lokalizaciju nedostataka i alociranje rezervnih ćelija. Ovaj pristup smanjuje prekomjernu i nedovoljnu aktivnost, poboljšavajući i prinos i dugoročnu pouzdanost.

U memorijskim proizvodima, Samsung Electronics implementirao je evaluaciju redundancije u stvarnom vremenu u svojim najnovijim DRAM i NAND flash linijama. Napredni krugovi za samopročišćavanje (BISR), povećani prediktivnom analitikom, omogućuju brzo identificiranje i zamjenu neispravnih ćelija tijekom razvrstavanja wafers, čak i kako se veličine nizova povećavaju na stotine gigabita. Ove inovacije minimiziraju rizik od latentnih neuspjeha nakon implementacije i optimiziraju korištenje redundantnih elemenata na čipu.

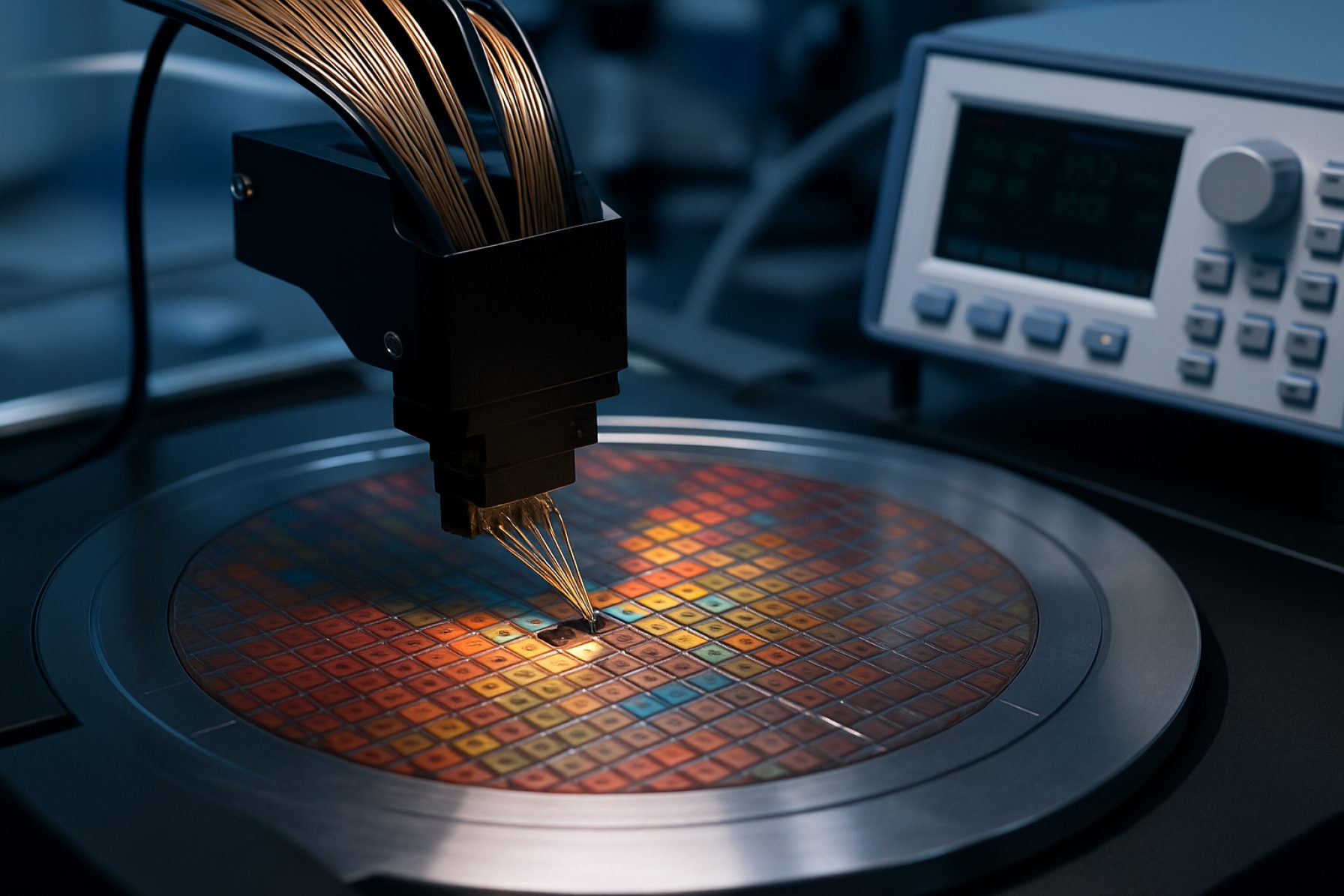

Dobavljači automatizirane testne opreme (ATE) kao što je Advantest Corporation uvode nove platforme koje imaju podršku za protokole testiranja usmjerene na redundanciju. Njihova serija V93000, lansirana 2024. godine, omogućuje paralelno testiranje i popravak na licu mjesta za višestupanjske pakete i čiplete – ključna značajka kako se napredno pakiranje širi u područjima visoko performansnog računarstva i aplikacija umjetne inteligencije.

Ecosustav opreme za poluvodiče reagira i na potrebu za ultraljubičastim testnim okruženjima. Lam Research izvještava o napretku u rukovanju wafers-i bez kontaminacije i procesnim komorama 2025. godine, što direktno podržava integritet testiranja redundancije za čipove najnovije generacije gdje čak i atomi kontaminacije mogu iskriviti podatke o prinosu ili maskirati latentne nedostatke redundancije.

Gledajući unaprijed, očekuje se konvergencija analitike podataka, ko-optimizacije hardvera i softvera i strožeg upravljanja procesima kako bi se dodatno poboljšalo testiranje redundancije. Integracija digitalnih blizanaca i prediktivne analitike temeljenih na AI je na horizontu, obećavajući gotovo nulti-defektne proizvodnje kako složenost uređaja raste. Suradnja između tvornica, proizvođača opreme i dizajnera bez tvornica bit će ključna za ostvarenje ovih napredaka i održavanje opskrbe ultrapurinim, ultra-pouzdanim poluvodičima.

Glavni igrači i strateški savezi (fokus na 2025.)

U 2025. godini, pejzaž testiranja ultrapurih poluvodiča karakterizira značajna aktivnost među glavnim igračima u industriji, strateškim partnerstvima i ulaganjima u napredna rješenja testiranja. Kako se čipovi nastavljaju smanjivati, potražnja za ultrapurim okruženjima i robusnim testiranjem redundancije se pojačava. Ključni igrači – uključujući proizvođače opreme, tvornice poluvodiča i dobavljače materijala – sve više surađuju kako bi se suočili s strožim zahtjevima za otkrivanje nedostataka i pouzdanost procesa.

- Applied Materials, Inc. ostaje na čelu, pružajući napredne platforme za inspekciju i metrologiju koje omogućuju testiranje redundancije na nanometarskim razmjerima. U 2025. godine, tvrtka je objavila proširenja u suradnji s vodećim proizvođačima logike i memorije kako bi zajednički razvili module za inspekciju redundancije sljedeće generacije optimizirane za ultrapura okruženja (Applied Materials, Inc.).

- ASML Holding NV nastavlja igrati ključnu ulogu, posebno kroz svoje EUV litografske sustave, koji zahtijevaju rigorozno testiranje redundancije kako bi osigurali operativnu stabilnost. Početkom 2025. godine, ASML je proširio svoj savez s vodećim proizvođačima čipova kako bi integrirao posebne rutine testiranja redundancije unutar EUV alata, s ciljem minimiziranja kontaminacije i neplaniranih zastoja (ASML Holding NV).

- Tokyo Electron Limited (TEL) produbio je svoja partnerstva s globalnim tvornicama i tvrtkama bez tvornica, fokusirajući se na zajedničku inovaciju za ultrapure procesne module i verifikaciju redundancije. TEL-ove inicijative iz 2025. uključuju zajedničke pilot programe s velikim tvornicama u Aziji kako bi se usavršili automatizirani algoritmi testiranja za kritično upravljanje prinosom (Tokyo Electron Limited).

- Samsung Electronics i TSMC—kao najveći svjetski proizvođači poluvodiča—obje su investirale u interne inovacije testiranja redundancije. U 2025., Samsung je objavio implementaciju AI-pokrenute platforme za praćenje redundancije na svojim naprednim logičkim linijama, dok je TSMC proširio svoj program kvalifikacije s više dobavljača redundancije kako bi uključio nove testne protokole za 2 nm procesne čipove (Samsung Electronics; TSMC).

- Industrijski savezi, poput onih koje koordinira SEMI, dodatno su ubrzali usklađivanje standarda testiranja i najboljih praksi, s novim radnim grupama u 2025. godini koje se fokusiraju isključivo na verifikaciju redundancije u ultrapurim proizvodnim okruženjima (SEMI).

Gledajući unaprijed, sektor će vjerojatno nastaviti vidjeti daljnju konvergenciju između dobavljača opreme i proizvođača uređaja, pri čemu će strateški savezi sve više biti usmjereni na zajednički razvoj prilagođenih, in-line rješenja za testiranje redundancije. Ovaj suradnički pristup vjerojatno će biti temelj sljedećeg vala inovacija u ultrapurim proizvodima poluvodiča, osiguravajući veće prinose i poboljšanu pouzdanost uređaja do 2026. godine i dalje.

Integracija lanaca opskrbe i izazovi čistoće

Testiranje redundancije u ultrapurim poluvodičima postaje ključni aspekt integracije lanaca opskrbe dok se industrija poluvodiča suočava sa sve strožim zahtjevima čistoće i rastućom složenošću u procesima proizvodnje. Kako se geometrije čipova smanjuju i osjetljivost uređaja na kontaminante povećava, osiguranje pouzdanosti i čistoće materijala i gotovih proizvoda kroz testiranje redundancije postalo je i tehnički i logistički izazov.

U 2025. godini, fokus je na integraciji naprednih protokola testiranja redundancije širom opskrbnog lanca. Glavne tvornice i dobavljači materijala sada zahtijevaju višestepeno testiranje ultrapurih plinova, kemikalija i silikonskih wafers na različitim procesnim čipovima kako bi se smanjio rizik od uvođenja nedostataka povezanih s neotkrivenim kontaminantima. Na primjer, Intel Corporation je skicirao strategije za redundantno inline i završno testiranje procesnih kemikalija kako bi osigurao da su greške ili kontaminacija u bilo kojoj fazi brzo otkrivene i izolirane prije nego što utječu na šire prinos.

Drugi ključni razvoj je zajednički napor za standardizaciju mjernih parametara čistoće i metodologija testiranja od strane industrijskih tijela poput SEMI. U 2024. i u 2025. godini, SEMI-jev program međunarodnih standarda radio je s proizvođačima čipova, dobavljačima opreme i dobavljačima kemikalija na usavršavanju protokola za redundantnu validaciju čistoće, uključujući dvostruko verifikovanje kemijskih serija i praćenje plinova u stvarnom vremenu. Takve inicijative direktno se bave integracijom opskrbnog lanca uspostavljanjem jedinstvenih očekivanja i zahtjeva za razmjenu podataka između dobavljača i proizvođača.

Vodeći dobavljači materijala poput Entegris i DuPont ulažu u napredne senzorske mreže i automatiziranu analitiku kako bi omogućili kontinuirane, redundantne provere čistoće. Ovi sustavi mogu pratiti kontaminante do razine dijelova po trilijunu, pružajući primjenjive podatke koji se dijele s partnerima nizvodno kao dio integriranog okvira osiguranja kvalitete. Ovo je posebno ključno dok industrija gleda prema procesnim čipovima ispod 2 nm, gdje čak i tragovi nečistoća mogu ugroziti integritet uređaja.

Gledajući naprijed, tijekom sljedećih nekoliko godina, vjerojatno će se testiranje redundancije također postati sve automatiziranije i dublje ugrađeno u sustave upravljanja digitalnim opskrbnim lancima. Tvrtke razvijaju rješenja za tragovnost temeljena na blockchainu i sigurne platforme za razmjenu podataka kako bi zabilježile i verifcirale svaki rezultat testa čistoće tijekom opskrbnog lanca, kako su pilotirali TSMC i njegovi partnerski ekosustavi. Ova digitalizacija će pomoći u identifikaciji potencijalnih prekida ili propusta u redundanciji prije nego što mogu utjecati na proizvodnju velikih količina, dodatno osiguravajući čistoću i pouzdanost naprednih poluvodiča.

Regulatorno okruženje i tijela za standarde (npr. SEMI.org, IEEE.org)

Regulatorno okruženje za testiranje redundancije u ultrapurim poluvodičima brzo se razvija dok se industrija suočava s tehnološkim napretkom i rastućim zahtjevima za pouzdanost uređaja. Ultrapuri uvjeti su kritični za izradu poluvodiča, pri čemu čak i mala kontaminacija ugrožava neuspjeh wafers-a ili latentne nedostatke uređaja. Testiranje redundancije – implementacija više metodologija testiranja ili rezervnih sustava – postalo je područje fokusa kako bi se osiguralo da su procesi testiranja sami dovoljno robusni da otkriju i ublaže moguće greške.

Ključne organizacije za razvoj standarda poput SEMI i IEEE igraju ključne uloge u oblikovanju regulatornog okruženja za testiranje redundancije. SEMI F63 standard, na primjer, obrađuje smjernice za kvalitetu ultrapurih voda (UPW) u proizvodnji poluvodiča, neizravno utječući na protokole redundancije specificirajući limite rizika od kontaminacije i zahtjeve monitoringa. U 2025. godini, SEMI nastavlja ažurirati standarde povezane s testiranjem i monitoringom UPW i plinskih sustava, koji su integralni za strategije redundancije u kritičnim procesnim koracima.

Slično tome, IEEE ima trenutne inicijative unutar svoje Udruge za standarde relevantne za ponovljivost metoda testiranja, toleranciju na greške sustava i redundanciju u kvalifikaciji poluvodičkih uređaja. IEEE 1687 (IJTAG) i povezani standardi doprinose okvirima za pristup ugrađenim instrumentima za praćenje redundancije i grešaka u stvarnom vremenu. Kako uređaji postaju složeniji i procesni čipovi se smanjuju, standardi testiranja sve više naglašavaju redundanciju ne samo u testnim rutinama, već i u arhitekturama možda ugrađenog samoprovođenja (BIST).

Posljednjih godina globalna regulatorna tijela i industrijske kohorte naglašavaju usklađivanje najboljih praksi. SEMI-jev program međunarodnih standarda, na primjer, olakšava prekogranično usklađivanje zahtjeva monitora i validacije redundancije, odražavajući globaliziranu prirodu opskrbnih lanaca poluvodiča. U 2025. godini, SEMI-jeve tehničke komisije prioritiziraju suradnju s regionalnim vlastima kako bi osigurale da protokoli testiranja redundancije zadovoljavaju i lokalne regulatorne zahtjeve i međunarodne standarde.

Gledajući naprijed u sljedeće nekoliko godina, očekuje se daljnje pooštravanje regulatornog okruženja. S proliferacijom aplikacija visoke pouzdanosti – poput automobilske, zrakoplovne i zdravstvene elektronike – vlasti će vjerojatno zahtijevati rigoroznije testiranje redundancije i dokumentaciju. Tijela za standarde poput SEMI i IEEE očekuje se da će objaviti nove smjernice koje se bave naprednim metodama verifikacije redundancije, s povećanim zahtjevima za digitalnom tragovnosti, prediktivnom analytikom i nadzorom testiranja vođenim AI. Sudionici u industriji trebaju ostati agilni, proaktivno se prilagođavajući tim evolucijskim standardima kako bi održali usklađenost i konkurentsku prednost.

Emergenta tržišta i regionalne prilike

Pejzaž za ultrapure testove redundancije poluvodiča brzo se razvija u 2025. godini, oblikovan globalnom ekspanzijom napredne proizvodnje čipova i rastućom složenošću integriranih krugova. Kako glavni proizvođači ulažu u čipove budućnosti – kao što su 3nm i manje – potražnja za strogim protokolima testiranja redundancije u ultrapurim環境ima raste, posebno u emergentnim središtima proizvodnje poluvodiča.

U 2025. godini dolazi do značajnog rasta u regiji Azija-Pacifik, uz Tajvan, Južnu Koreju i kineski kopneni dio koji prednjače u ulaganjima u nove kapacitete tvornica. Taiwan Semiconductor Manufacturing Company (TSMC) i Samsung Electronics proširuju svoje napredne procesne sposobnosti s jakim fokusom na smanjenje kontaminacije i osiguranje redundancije u kritičnim procesnim koracima. Ove tvrtke integriraju napredno testiranje redundancije kako bi udovoljavale sve rigoroznijim standardima za iincrementacijske performanse i pouzdanost, posebno u automobilskoj i AI-orijentiranim čipovima.

U međuvremenu, Sjedinjene Američke Države svjedoče o ponovnom porastu u proizvodnji poluvodiča, potpomognute saveznicima na saveznoj razini i partnerstvima s lokalnim dobavljačima. Intel aktivno gradi nove tvornice u Arizoni i Ohiju, usmjeravajući se na implementaciju sustava testiranja redundancije za ultrapure procesne tokove. Ovi sustavi koriste inspekciju grešaka na mjestu i analitiku u stvarnom vremenu kako bi otkrili i umanjili potencijalne jedinstvene točke neuspjeha, čime se povećava prinos i pouzdanost za kritične aplikacije.

U Europi, pojava novih objekata od strane GlobalFoundries i daljnji rast Infineon Technologies potiču potražnju za najmodernijim testovima redundancije. “Zakon o čipovima” Europske unije ima za cilj udvostručiti proizvodnju čipova u regiji do 2030. godine, potičući ulaganja u ultrapuru vodu, plinove i tehnologije kontrole kontaminacije koje ovise o robustnim testovima redundancije kako bi se zadovoljili strogi standardi kvalitete.

Dobavljači tehnologije specijalizirani za testiranje redundancije – kao što su Advantest Corporation i Teradyne – prijavljuju povećane narudžbe kako od etabliranih tvornica, tako i od novih ulazaka u ovim regijama. Njihova rješenja sve više su prilagođena visokom prohodnosti i otkrivanju ultra-niskih razina kontaminanata i latentnih nedostataka, s očekivanjem da će analitika vođena AI postati standard u sljedećih nekoliko godina.

Gledajući unaprijed, emergentna tržišta u jugoistočnoj Aziji, Indiji i Bliskom Istoku postavljaju se da razviju vlastite napredne proizvodne ekosustave. Kako ove regije povećavaju kapacitete, potražnja za ultrapurinim testovima redundancije će se povećati, potičući globalnu suradnju i usvajanje najbolje tehnologije kako bi se osigurala dosljedna kvaliteta i prinos suočeni s rastućom složenošću čipova.

Strateški pregled: Disruptivne tehnologije i long-term trendovi

Testiranje redundancije u ultrapurim poluvodičima je na čelu osiguravanja pouzdanosti jer se geometrije uređaja nastavljaju smanjivati, a složenosti tvornica povećavaju. Do 2025. godine, strateški pregled ovog područja oblikuje se snažno konvergencijom disruptivnih tehnologija i pomacima industrije prema proizvodnji bez nedostataka, potaknutih zahtjevima AI, automobila i naprednih logičkih aplikacija.

Vodeći proizvođači poluvodiča brzo evoluiraju svoje metodologije testiranja redundancije kako bi zadovoljili više standarde čistoće i prinosa. Na primjer, TSMC je istaknula svoju predanost naprednom poboljšanju prinosa i rigoroznom otkrivanju nedostataka u svojim najnovijim procesnim tehnologijama, integrirajući testiranje redundancije u stvarnom vremenu i AI-pokrenutu analitiku izravno u svoje proizvodne linije. Slično tome, Intel ulaže u sustave za validaciju redundancije u stvarnom vremenu, koristeći strojnog učenja za predikciju i izolaciju latentnih neuspjeha u svojim proizvodnim tokovima za čipove 18A i 20A.

Značajan trend u 2025. godini je usvajanje naprednih metrologijskih i inspekcijskih alata sposobnih otkriti atomi-takve nedostatke u ultrapurim okruženjima. Applied Materials i Lam Research, među vodećim dobavljačima opreme za poluvodiče, primenjuju inspekcijske platforme koje kombiniraju e-zračenje, duboko učenje i protokole algoritmo-potryenih pravaca za osiguranje da se ekskurzije procesa mogu brzo sadržati i korigirati. Ovi sustavi mogu otkriti i karakterizirati sub-nanometarske kontaminacije i električne greške, što je od velike važnosti za validaciju redundancije kod memorijskih i logičkih čipova.

Još jedan disruptivni trend je integracija testiranja redundancije u smart manufacturing platforme. Samsung Semiconductor upravlja pilot projektom AI-pokretne platforme za praćenje redundancije integrirane s digitalnim blizancima svojih tvornica, omogućujući prediktivno održavanje i trenutnu prilagodbu procesa. To smanjuje vrijeme zastoja i povećava pouzdanost proizvodnje naprednih čipova, izravno se obraćajući očekivanjima bez nedostatka na tržištima automobila i podatkovnih centara.

Gledajući unaprijed, strateški pregled za ultrapure testiranje redundancije poluvodiča uključuje daljnju automatizaciju i analitiku temelje na oblaku. Industrijski konzorciji poput SEMI postavljaju nove standarde za interoperabilnost protokola testiranja i razmjenu podataka širom opskrbnog lanca, s ciljem pojednostavljenja verificiranja redundancije od razine wafers do sustava. Kako tvornice povećavaju oslanjanje na napredno testiranje redundancije, očekujte daljnje suradnje između proizvođača opreme, proizvođača čipova i dobavljača materijala kako bi se ubrzalo eliminaciju nedostataka zatvorenog kruga i pomakao granice pouzdanosti uređaja do 2025. godine i dalje.

Izvori i reference

- imec

- Advantest Corporation

- STMicroelectronics

- Synopsys

- ASML

- Infineon Technologies

- BASF

- DuPont

- Tokyo Electron Limited

- Samsung Electronics

- Entegris

- IEEE