Spis treści

- Podsumowanie wykonawcze: 2025 i droga przed nami

- Wielkość rynku i prognozy wzrostu do 2030 r.

- Kluczowe czynniki: AI, IoT i zaawansowana produkcja węzłów

- Standardy ultrapure: ewoluujące wymagania i benchmarki branżowe

- Najnowocześniejsze innowacje w metodach testowania redundancji

- Najwięksi gracze i sojusze strategiczne (skupienie na 2025 r.)

- Integracja łańcucha dostaw i wyzwania związane z czystością

- Środowisko regulacyjne i organy normalizacyjne (np. SEMI.org, IEEE.org)

- Rynki wschodzące i regionalne możliwości

- Perspektywy strategiczne: technologie zakłócające i długoterminowe trendy

- Źródła i odniesienia

Podsumowanie wykonawcze: 2025 i droga przed nami

Testy redundancji ultrapure w półprzewodnikach zyskują krytyczną dynamikę, gdy branża wchodzi w 2025 rok, napędzane nieustannym dążeniem do mniejszych węzłów, wyższej niezawodności urządzeń oraz proliferacją zaawansowanych aplikacji, takich jak AI, elektronika motoryzacyjna i obliczenia kwantowe. Środowiska ultrapure są niezbędne do osiągnięcia surowych wymagań dotyczących wydajności i niezawodności w produkcji chipów sub-5nm i następnej generacji. Testowanie redundancji – gdzie obwody zapasowe i architektury odporne na awarie są systematycznie weryfikowane – stało się kluczowym elementem zapewniającym odporność produkcyjną, minimalizując kosztowne przestoje oraz radząc sobie z ukrytymi wadami, które mogą wynikać nawet z mikroskopijnych zanieczyszczeń lub wariacji procesu.

Wiodący producenci półprzewodników zwiększają inwestycje w testowanie redundancji w ultrapure środowiskach. Na przykład, Taiwan Semiconductor Manufacturing Company (TSMC) nadal rozszerza swoje skupienie na walidacji redundancji jako części swoich strategii kontroli procesów zaawansowanych i zarządzania wadami, szczególnie w swoich węzłach 3nm i 2nm. Podobnie, Samsung Electronics Semiconductor podkreśla integrację mechanizmów redundancji i wyrafinowanych protokołów testowych w swoich nowoczesnych fabach, dążąc do dalszego wzmocnienia niezawodności urządzeń, gdy przechodzi do architektur tranzystorów gate-all-around (GAA).

Dostawcy sprzętu również dostosowują się do tych wymagań. Applied Materials i Lam Research wprowadzają innowacyjne narzędzia do inspekcji wafli i metrologii, które wykorzystują analitykę opartą na AI do wykrywania i charakteryzowania usterek redundancji bardziej efektywnie w ultrapure liniach procesowych. Systemy te są uruchamiane, aby monitorować defekty indukowane procesem i weryfikować integralność operacyjną struktury redundantnej.

Dane z konsorcjów branżowych, takich jak SEMI, wskazują, że inwestycje w testowanie i metrologię zaawansowanych schematów redundancji mają rosnąć w tempie CAGR przekraczającym 7% do 2028 roku, co odzwierciedla priorytetyzację zarządzania wydajnością i zapewnienia niezawodności w tym sektorze. Ponadto, wspólne wysiłki, takie jak te w imec, przyspieszają rozwój nowatorskich architektur redundancji i protokołów produkcyjnych dostosowanych do ultrapure środowisk.

Patrząc w przyszłość, w następnych kilku latach testowanie redundancji stanie się coraz bardziej zautomatyzowane, skoncentrowane na danych oraz ściśle zintegrowane z kontrolą procesów w czasie rzeczywistym. W miarę jak producenci półprzewodników dążą do 2nm i dalej, paradygmat zerowej wady będzie zależał od postępów zarówno w projektowaniu, jak i testowaniu redundancji w ultrapure ustawieniach. Ta ewolucja będzie kluczowa dla utrzymania niezawodności, skalowalności oraz komercyjnej opłacalności przyszłych technologii półprzewodnikowych.

Wielkość rynku i prognozy wzrostu do 2030 r.

Globalny rynek testowania redundancji ultrapure w półprzewodnikach jest gotowy na znaczny wzrost do 2030 roku, napędzany rosnącą złożonością urządzeń półprzewodnikowych, proliferacją zaawansowanych węzłów (5nm, 3nm i poniżej) oraz rosnącym popytem na ultra-niezawodne chipy w kluczowych aplikacjach, takich jak motoryzacja, centra danych i AI. W miarę jak geometrie urządzeń maleją, a poziomy integracji rosną, konieczność zapewnienia absolutnej czystości i niezawodności w procesach produkcji półprzewodników postawiła testowanie redundancji na czołowej pozycji w zapewnieniu jakości.

W 2025 roku wiodący producenci półprzewodników, tacy jak Taiwan Semiconductor Manufacturing Company (TSMC), Samsung Electronics i Intel Corporation, nadal rozszerzają swoje inwestycje w zaawansowaną infrastrukturę testowania redundancji. Inwestycje te mają na celu nie tylko wykrywanie i łagodzenie ukrytych wad w układach logicznych i pamięci, ale także spełnianie coraz surowszych wymagań dotyczących niezawodności, jakie stawiają sektory motoryzacyjne i krytyczne dla misji. Na przykład ciągłe rozszerzenia zdolności TSMC i ich skupienie na inicjatywach „Zero Defect” podkreślają centralność ultrapure środowisk testowych w ich planie rozwoju.

Równolegle do inwestycji w fabrykach główni dostawcy sprzętu testowego, tacy jak Advantest Corporation i Teradyne, Inc., szybko wprowadzają innowacje, aby dostarczyć rozwiązania automatycznego sprzętu testowego (ATE) nowej generacji, zdolne do wspierania testów redundancji w procesach węzłów nanometrowych. Te systemy coraz częściej wykorzystują analitykę opartą na AI oraz testowanie równoległe o wysokiej wydajności w celu poprawy pokrycia i redukcji wskaźników niepowodzeń testów, dostosowując się do ewoluujących potrzeb zaawansowanych fabryk.

Zgodnie z niedawnymi ujawnieniami korporacyjnymi i mapami drogowymi branży, rynek ultrapure sprzętu do testowania redundancji półprzewodników i usług ma wzrosnąć w tempie CAGR w okolicach wysokich jednocyfrowych wartości do 2030 roku, przy czym region Azji-Pacyfiku – zdominowany przez Tajwan, Koreę Południową i Chiny – pozostaje głównym silnikiem popytu. Rozbudowa nowych fabryk („mega fab”) przez Samsung Electronics i TSMC w latach 2025-2027 dodatkowo podkreśla silne perspektywy sektora.

Patrząc w przyszłość, przyjęcie litografii ekstremalnej ultrafioletowej (EUV), heterogenicznej integracji i architektur chipletów będzie prowadziło do jeszcze większego uzależnienia od metod testowania redundancji ultrapure. Wspólne wysiłki między producentami, dostawcami sprzętu i stowarzyszeniami branżowymi, takimi jak SEMI, mają przyspieszyć rozwój norm i najlepszych praktyk, zapewniając, że testowanie redundancji nadąża za skalowaniem technologii i wymaganiami niezawodnościowymi do 2030 roku i później.

Kluczowe czynniki: AI, IoT i zaawansowana produkcja węzłów

Szybki rozwój sztucznej inteligencji (AI), Internetu rzeczy (IoT) i zaawansowanej produkcji węzłów znacząco przyspiesza popyt na testowanie redundancji ultrapure w półprzewodnikach. W miarę jak złożoność urządzeń i gęstość integracji rośnie, szczególnie w węzłach poniżej 5nm, zapewnienie odporności na awarie i niezawodnej pracy staje się kluczowe. Akceleratory AI, na przykład, wymagają obecnie solidnych testów redundancji, aby osiągnąć niskie wskaźniki defektów niezbędne w aplikacjach krytycznych dla misji w sektorze motoryzacyjnym, medycznym i przemysłowym. Zarówno Intel Corporation, jak i Taiwan Semiconductor Manufacturing Company zgłaszają coraz większe skupienie na zaawansowanych schematach redundancji i protokołach testowych dla swoich najnowszych węzłów procesowych, co odzwierciedla ogólną zmianę w branży w kierunku zwiększonej niezawodności.

Proliferacja IoT dodatkowo amplifikuje potrzeby związane z testowaniem redundancji. Z miliardami połączonych czujników i urządzeń przewidywanych do 2025 roku, producenci muszą zapewnić ciągłość działania i bezpieczeństwo, nawet w obliczu częściowych awarii sprzętowych. STMicroelectronics podkreśla, że ich półprzewodniki ukierunkowane na IoT przechodzą rozszerzone testy redundancji i niezawodności, korzystając z automatycznego sprzętu testowego zdolnego do symulowania złożonych trybów awarii.

Wprowadzenie architektur chipletów i pakowania 3D na zaawansowanych węzłach również przekształca metody testowania. Złożone systemy multi-die wymagają nie tylko tradycyjnych testów funkcjonalnych, ale także weryfikacji redundancji na poziomie całego systemu w ramach połączonych dies. Advanced Micro Devices (AMD) przyjęło nowe strategie projektowania z myślą o testach, które uwzględniają redundancję (DFT) dla swoich procesorów opartych na chipletach, podczas gdy Synopsys oraz Advantest wdrażają rozwiązania testowe nowej generacji, aby odpowiedzieć na unikalne wymagania dotyczące odporności na awarie tych architektur.

- Dane i trendy (2025 i później): Firmy fabless oraz fabryki zwiększają swoje budżety na pokrycie testów i badania redundancji, z odnotowanym wzrostem wydatków na zaawansowany sprzęt testowy o 18% rok do roku (ASML). Punkty wstawiania testów waferów i ostatecznych pakietów rozszerzają się, szczególnie dla chipów przeznaczonych do aplikacji AI i krytycznej dla bezpieczeństwa IoT.

- Perspektywy: W ciągu kilku najbliższych lat przewiduje się, że producenci półprzewodników dalej skorzystają z generowania wzorców testowych napędzanych przez AI oraz adaptacyjnych strategii redundancji, co zmniejszy testowe ucieczki i poprawi niezawodność w terenie. Integracja monitorowania redundancji w czasie rzeczywistym w wdrożonych urządzeniach — umożliwiająca dzięki AI na krawędzi i cyfrowym bliźniakom — przekształci granice wykrywania i korekcji awarii w polu (Infineon Technologies).

Podsumowując, zbieżność AI, IoT i zaawansowanej produkcji węzłów zmusza branżę do redefiniowania paradygmatów testowania redundancji ultrapure w półprzewodnikach, z istotnymi inwestycjami i innowacjami, przewidzianymi na lata 2025 i później.

Standardy ultrapure: ewoluujące wymagania i benchmarki branżowe

Testowanie redundancji ultrapure staje się fundamentem produkcji półprzewodników, gdy geometrie urządzeń wciąż maleją, a złożoność funkcjonalna wzrasta. Konieczność zapewnienia nieprzerwanego dostępu do ultrapure wody (UPW), chemikaliów oraz gazów napędza nowe standardy i benchmarki dla testowania redundancji w całej branży. W 2025 roku sektor ten jest świadkiem zbieżności rygorystycznej kontroli procesów, automatyzacji oraz analizy danych, aby utrzymać te wymagania.

Wiodący producenci wdrażają wielowarstwową redundancję w swoich ultrapure systemach, aby zminimalizować ryzyko zanieczyszczenia lub przestoju. Na przykład, Intel informuje, że jego zakłady produkcyjne wafli obecnie stosują podwójne pętle UPW, równoległe układy filtracyjne i czujniki w czasie rzeczywistym, które automatycznie przełączają się na systemy zapasowe, jeśli wykryta zostanie odchylenie. Ta redundancja jest ciągle testowana pod kątem wytrzymałości poprzez symulacje i ćwiczenia na żywo, zapewniając, że wszystkie krytyczne węzły mogą utrzymać czystość klasy półprzewodników (<18 MΩ·cm dla UPW) nawet w trudnych sytuacjach.

Z drugiej strony dostawcy chemikaliów, tacy jak BASF i DuPont, współpracują z producentami urządzeń, aby zweryfikować redundantną infrastrukturę dostaw i magazynowania. Systemy te przechodzą okresowe testy wyzwań, w których główny dostawca jest celowo przerywany, a automatyczne przełączenie na zapas jest monitorowane zarówno pod kątem szybkości, jak i zapewnienia czystości. Dane z tych testów są dzielone z klientami, stanowiąc część audytów jakości dostawcy i zgodności z normami branżowymi, takimi jak SEMI F63 oraz wytycznymi ITRS (SEMI).

Perspektywy na następne kilka lat wskazują na dalsze zaostrzenie benchmarków. Organizacja SEMI aktywnie aktualizuje swoje standardy dotyczące walidacji redundancji, kładąc nacisk na cyfrową trasowalność, rejestrowanie zdarzeń oraz analitykę predykcyjną awarii. Dostawcy sprzętu, tacy jak Evoqua Water Technologies, oferują już zintegrowane pakiety testowe, łączące testy fizycznego przełączania z diagnostyką opartą na chmurze, aby zapewnić ciągłe potwierdzenie.

Dążenie do technologii procesów poniżej 2 nm ma prowadzić do jeszcze bardziej rygorystycznych protokołów testowania redundancji. Wymiana danych w czasie rzeczywistym między producentami a dostawcami, jak pokazują ostatnie inicjatywy TSMC, staje się standardową praktyką. To współprace podejście nie tylko zwiększa odporność, ale również zapewnia szybki reagowanie na nieprawidłowości, ustalając nowe benchmarki branżowe dla niezawodności i integralności procesów w środowisku, w którym każde uchybienie może mieć multimilionowe konsekwencje finansowe.

Najnowocześniejsze innowacje w metodach testowania redundancji

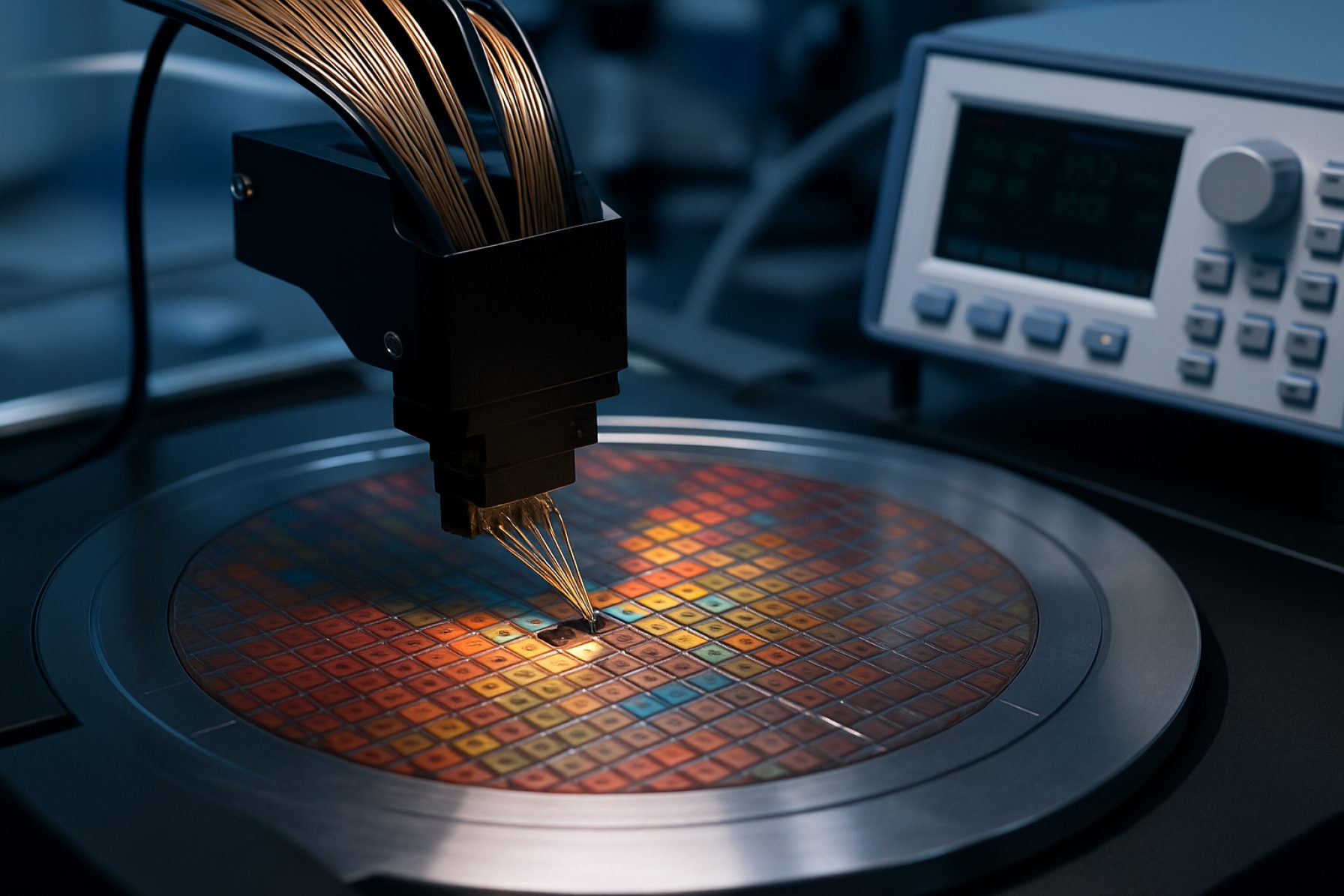

Produkcja ultrapure półprzewodników wciąż przesuwa granice wydajności urządzeń, a metody testowania redundancji szybko ewoluują, aby zapewnić niezawodność w coraz bardziej złożonych układach scalonych (IC). W miarę zaawansowania geometrii urządzeń oraz rosnących wymagań dotyczących ultra-wysokiej wydajności, testowanie redundancji – zwłaszcza w pamięciach i logice – stało się centralnym punktem innowacji.

W 2025 roku wiodący producenci półprzewodników wdrażają zaawansowane rozwiązania analizy i naprawy redundancji zintegrowane w ich procesach testowych. Na przykład Taiwan Semiconductor Manufacturing Company (TSMC) podkreśla wykorzystanie adaptacyjnych algorytmów redundancji w swoich węzłach procesowych 3nm i 2nm, wykorzystując dane z testów w locie oraz uczenie maszynowe do dynamicznego lokalizowania defektów i alokacji komórek zapasowych. Takie podejście redukuje nadmiarowe i niewystarczające działania, zwiększając zarówno wydajność, jak i długoterminową niezawodność.

W produktach pamięci Samsung Electronics wdrożył ocenę redundancji w czasie rzeczywistym w swoich najnowszych liniach DRAM i NAND flash. Zaawansowane obwody do samonaprawy (BISR), wspierane przez analitykę predykcyjną, umożliwiają szybką identyfikację i wymianę uszkodzonych komórek podczas selekcji wafli, nawet gdy rozmiary macierzy przekraczają setki gigabitów. Te innowacje minimalizują ryzyko ukrytych awarii po wdrożeniu i optymalizują wykorzystanie elementów redundanckich na chipie.

Dostawcy automatycznego sprzętu testowego (ATE), tacy jak Advantest Corporation, wprowadzają nowe platformy z natywnym wsparciem dla protokołów testowych uwzględniających redundancję. Ich seria V93000, wprowadzone na rynek w 2024 roku, umożliwia równoległe testowanie i naprawę na miejscu dla pakietów wielodowych i chipletów – kluczowa cecha, gdy zaawansowane pakowanie się rozwija w aplikacjach wydajnościowych i sztucznej inteligencji.

Ekosystem sprzętu półprzewodnikowego także odpowiada na potrzeby ultraczystych środowisk testowych. Lam Research zgłasza postępy w obsłudze wafli wolnej od zanieczyszczeń oraz komór procesowych w 2025 roku, bezpośrednio wspierając integralność testowania redundancji dla węzłów najnowszej generacji, gdzie nawet zanieczyszczenia na poziomie atomowym mogą zakłócać dane dotyczące wydajności lub maskować ukryte wady redundancji.

Patrząc w przyszłość, konwergencja analityki danych, współoptymalizacji sprzętu i oprogramowania oraz ściślejszej kontroli procesów ma jeszcze bardziej zwiększyć testowanie redundancji. Integracja cyfrowych bliźniaków i przewidywania defektów opartego na AI jest na horyzoncie, obiecując produkcję z niemal zerową ilością defektów, gdy złożoność urządzeń rośnie. Współpraca między fabrykami, producentami sprzętu a projektantami fabless będzie niezbędna do realizacji tych postępów i utrzymania dostaw ultrapure, ultra-niezawodnych półprzewodników.

Najwięksi gracze i sojusze strategiczne (skupienie na 2025 r.)

W 2025 roku krajobraz testowania redundancji ultrapure w półprzewodnikach charakteryzuje się znaczną aktywnością wśród kluczowych graczy branżowych, strategicznych partnerstw oraz inwestycji w zaawansowane rozwiązania testowe. W miarę jak węzły w produkcji półprzewodników wciąż się zmniejszają, popyt na ultrapure środowiska oraz solidne testy redundancji nasila się. Kluczowe firmy – w tym producenci sprzętu, fabryki półprzewodników oraz dostawcy materiałów – coraz częściej współpracują, aby spełnić surowe wymagania dotyczące wykrywania wad i niezawodności procesów.

- Applied Materials, Inc. pozostaje na czołowej pozycji, dostarczając zaawansowane platformy inspekcji i metrologii, które umożliwiają testowanie redundancji na nanometrowych skalach. W 2025 roku firma ogłosiła rozszerzenia współpracy z wiodącymi producentami logicznych i pamięci, aby współtworzyć moduły inspekcji redundancji nowej generacji, zoptymalizowane dla ultrapure warunków (Applied Materials, Inc.).

- ASML Holding NV nadal odgrywa kluczową rolę, szczególnie poprzez swoje systemy litografii EUV, które wymagają rygorystycznego testowania redundancji w linii, aby zapewnić stabilność operacyjną. Na początku 2025 roku ASML rozszerzył swoje sojusze z wiodącymi producentami chipów, aby zintegrować proprietarne procedury testów redundancji w zestawach narzędzi EUV, dążąc do minimalizacji zanieczyszczenia i nieplanowanych przestojów (ASML Holding NV).

- Tokyo Electron Limited (TEL) pogłębił swoje partnerstwa z globalnymi fabrykami i firmami fabless, koncentrując się na współinowacji dla ultrapure modułów procesowych oraz weryfikacji redundancji. Inicjatywy TEL w 2025 roku obejmują wspólne programy pilotażowe z głównymi fabrykami w Azji, mające na celu udoskonalenie algorytmów testowania zautomatyzowanego dla krytycznego zarządzania wydajnością (Tokyo Electron Limited).

- Samsung Electronics i TSMC — jako największe na świecie firmy produkujące półprzewodniki — zainwestowały w wewnętrzne innowacje testowania redundancji. W 2025 roku Samsung ogłosił wdrożenie platformy monitorowania redundancji napędzanej przez AI w swoich zaawansowanych liniach logicznych, podczas gdy TSMC rozszerzyło swój program kwalifikacji redundancji wielokrotnego dostawcy o nowe protokoły testowe dla węzłów procesowych 2 nm (Samsung Electronics; TSMC).

- Sojusze branżowe, takie jak te koordynowane przez SEMI, dodatkowo przyspieszyły harmonizację standardów testowania i najlepszych praktyk. W 2025 roku nowe grupy robocze koncentrują się szczególnie na weryfikacji redundancji w ultrapure środowiskach produkcyjnych (SEMI).

Patrząc w przyszłość, sektor przewiduje dalszą konwergencję między dostawcami sprzętu a producentami urządzeń, z sojuszami strategicznymi coraz częściej skoncentrowanymi na współtworzeniu dostosowanych, liniowych rozwiązań testowych redundancji. Takie współprace podejście prawdopodobnie stanowią fundament nadchodzącej fali innowacji w ultrapure produkcji półprzewodników, zapewniając wyższe wydajności i zwiększoną niezawodność urządzeń do 2026 roku i później.

Integracja łańcucha dostaw i wyzwania związane z czystością

Testowanie redundancji ultrapure w półprzewodnikach staje się kluczowym aspektem integracji łańcucha dostaw, gdy branża półprzewodnikowa staje w obliczu coraz bardziej zaostrzonych wymagań dotyczących czystości i rosnącej złożoności w procesach produkcyjnych. W miarę jak geometrie chipów maleją, a wrażliwość urządzeń na zanieczyszczenia wzrasta, zapewnienie niezawodności i czystości zarówno materiałów, jak i produktów gotowych poprzez testowanie redundancji stało się zarówno technicznym, jak i logistycznym wyzwaniem.

W 2025 roku skupienie się na integracji zaawansowanych protokołów testowania redundancji w całym łańcuchu dostaw staje się kluczowe. Główne fabryki i dostawcy materiałów teraz nakładają wymóg wieloetapowego testowania ultrapure gazów, chemikaliów i wafli krzemowych na różnych węzłach przetwarzania, aby zminimalizować ryzyko wprowadzenia defektów spowodowanych niewykrytymi zanieczyszczeniami. Przykładowo, Intel Corporation sformułował strategie dotyczące redundacyjnego testowania w linii i punktów końcowych dla chemikaliów procesowych, aby zapewnić szybką detekcję i izolację wszelkich awarii czy zanieczyszczeń przed wpłynięciem na szersze wydajności produkcyjne.

Kolejnym istotnym rozwojem jest wspólny nacisk na standaryzację metryk czystości i metod testowania przez organizacje branżowe, takie jak SEMI. W latach 2024 i 2025 program międzynarodowych norm SEMI współpracował z producentami chipów, dostawcami sprzętu i dostawcami chemikaliów, aby udoskonalić protokoły walidacji czystości redundancji, w tym podwójną weryfikację partii chemikaliów oraz monitorowanie w czasie rzeczywistym gazów. Inicjatywy te bezpośrednio odpowiadają na integrację łańcucha dostaw, ustalając jednolite oczekiwania i wymogi dotyczące wymiany danych między dostawcami a producentami.

Wiodący dostawcy materiałów, tacy jak Entegris oraz DuPont, inwestują w zaawansowane sieci czujników i automatyczną analitykę, aby umożliwić ciągłe, redundantne kontrole czystości. Systemy te mogą śledzić zanieczyszczenia na poziomie parts-per-trillion, dostarczając danych przydatnych do podjęcia działań, które są dzielone z partnerami downstream w ramach zintegrowanego systemu zapewnienia jakości. Jest to szczególnie istotne w miarę, jak branża zmierza ku węzłom procesów poniżej 2nm, gdzie nawet śladowe zanieczyszczenia mogą zagrażać integralności urządzenia.

Patrząc w przyszłość, w następnych latach prawdopodobnie testowanie redundancji stanie się nie tylko bardziej zautomatyzowane, ale także głębiej zakorzenione w cyfrowych systemach zarządzania łańcuchem dostaw. Firmy opracowują rozwiązania z zakresu śledzenia oparte na blockchain oraz bezpieczne platformy wymiany danych, aby rejestrować i weryfikować wyniki każdego testu czystości w całym łańcuchu dostaw, co jest pilotowane przez TSMC i jego partnerów ekosystemu. Ta cyfryzacja pomoże zidentyfikować potencjalne awarie czy uchybienia w redundancji zanim wpłyną one na produkcję wysokowoluminalną, zabezpieczając jeszcze lepiej czystość i niezawodność zaawansowanych półprzewodników.

Środowisko regulacyjne i organy normalizacyjne (np. SEMI.org, IEEE.org)

Środowisko regulacyjne dla testowania redundancji ultrapure w półprzewodnikach szybko się zmienia w miarę tego, jak branża staje w obliczu zarówno postępu technologicznego, jak i rosnących wymagań dotyczących niezawodności urządzeń. Środowiska ultrapure są krytyczne dla wytwarzania półprzewodników, przy nawet najmniejszym zanieczyszczeniu grożącym awarią wafla lub latentnymi defektami urządzenia. Testowanie redundancji – wdrażanie wielu metod testowych lub systemów zapasowych – stało się obszarem ciężkiej pracy, aby zapewnić, że procesy testów same są wystarczająco solidne, by wykrywać i łagodzić możliwe usterki.

Kluczowe organizacje zajmujące się rozwojem standardów, takie jak SEMI i IEEE, odgrywają kluczowe role w kształtowaniu regulacyjnego otoczenia dla testowania redundancji. Na przykład standard SEMI F63 odnosi się do wytycznych dotyczących jakości ultrapure wody (UPW) w produkcji półprzewodników, pośrednio wpływając na protokoły redundancji poprzez określenie granic ryzyka zanieczyszczenia i wymagań dotyczących monitorowania. W 2025 roku SEMI nadal aktualizuje normy związane z testowaniem i monitorowaniem systemów UPW i gazów, które są integralne dla strategii redundancji w kluczowych etapach procesów.

Podobnie, IEEE prowadzi ciągłe inicjatywy w swojej organizacji normalizacyjnej, które mają zastosowanie do powtarzalności metod testowych, tolerancji na usterki systemów oraz redundancji w kwalifikacji urządzeń półprzewodnikowych. Standardy IEEE 1687 (IJTAG) i pokrewne standardy przyczyniają się do ram dostępu do zintegrowanych instrumentów w celu monitorowania redundancji i usterek w czasie rzeczywistym. W miarę jak urządzenia stają się coraz bardziej złożone, a węzły procesowe maleją, standardy testowania coraz bardziej kładą nacisk na redundancję nie tylko w procedurach testowych, ale także w architekturach wbudowanego testu (BIST) na chipach.

W ostatnich latach globalne organy regulacyjne i konsorcja branżowe kładły nacisk na harmonizację najlepszych praktyk. Program międzynarodowych norm SEMI, na przykład, ułatwia graniczny alignemnt w zakresie wymagań monitorowania i walidacji redundancji, odzwierciedlając globalny charakter łańcuchów dostaw półprzewodników. W 2025 roku techniczne komitety SEMI priorytetowo traktują współpracę z lokalnymi organami w celu zapewnienia, że protokoły testowania redundancji spełniają zarówno lokalne wymagania regulacyjne, jak i międzynarodowe normy.

Patrząc w przyszłość na najbliższe lata, przewiduje się, że środowisko regulacyjne ulegnie dalszemu zaostrzeniu. Wraz z proliferacją aplikacji o wysokiej niezawodności – takich jak elektronika motoryzacyjna, lotnicza i medyczna – władze prawdopodobnie będą wymuszać bardziej rygorystyczne testowania redundancji i dokumentację. Ciała normalizacyjne, takie jak SEMI i IEEE, przewidują wydanie nowych wytycznych dotyczących zaawansowanych metod weryfikacji redundancji, zwiększając wymagania dotyczące cyfrowej trasowalności, analityki predykcyjnej oraz nadzoru testowego opartego na AI. Uczestnicy rynków będą musieli pozostać elastyczni, proaktywnie dostosowując się do tych ewoluujących standardów, aby utrzymać zgodność i przewagę konkurencyjną.

Rynki wschodzące i regionalne możliwości

Krajobraz testowania redundancji ultrapure w półprzewodnikach szybko ewoluuje w 2025 roku, kształtowany przez globalną ekspansję zaawansowanej produkcji chipów oraz rosnącą złożoność zintegrowanych obwodów. W miarę jak główne fabryki inwestują w węzły nowej generacji – takie jak 3nm i poniżej – popyt na rygorystyczne protokoły testowania redundancji w ultrapure środowiskach rośnie, szczególnie w wschodzących centrach produkcji półprzewodników.

W 2025 roku znaczący wzrost odnotowano w regionie Azji-Pacyfiku, gdzie Taiwan, Korea Południowa oraz Chiny kontynentu prowadzą inwestycje w nową zdolność fabryczną. Taiwan Semiconductor Manufacturing Company (TSMC) oraz Samsung Electronics rozszerzają swoje możliwości procesowe, mocno koncentrując się na minimalizacji zanieczyszczenia oraz zapewnieniu redundancji w kluczowych etapach procesów. Firmy te integrują zaawansowane testowanie redundancji, aby spełnić coraz bardziej rygorystyczne standardy dotyczące defektywności i niezawodności, szczególnie w chipach motoryzacyjnych i centrach AI.

Równocześnie Stany Zjednoczone dostrzegają ożywienie w produkcji półprzewodników, napędzane przez federalne dotacje oraz partnerstwa z lokalnymi dostawcami. Intel aktywnie buduje nowe fabryki w Arizonie i Ohio, z naciskiem na wdrażanie systemów testowania redundancji dla ultrapure procesów. Systemy te wykorzystują inspekcję w linii defektów oraz analitykę w czasie rzeczywistym do wykrywania i łagodzenia potencjalnych punktów pojedynczych awarii, co podnosi wydajność i niezawodność w aplikacjach krytycznych.

W Europie powstanie nowych obiektów przez GlobalFoundries oraz dalszy rozwój Infineon Technologies napędzają popyt na nowoczesne testy redundancji. Akt „Chips Act” Unii Europejskiej ma na celu podwojenie produkcji chipów w regionie do 2030 roku, co pociąga za sobą inwestycje w ultrapure wodę, gazy oraz technologie kontroli zanieczyszczeń, które opierają się na solidnym testowaniu redundancji w celu spełnienia surowych wymogów jakości.

Dostawcy technologii specjalizujący się w testowaniu redundancji – tacy jak Advantest Corporation oraz Teradyne – zgłaszają zwiększone zamówienia zarówno od ugruntowanych fabryk, jak i nowych uczestników w tych regionach. Ich rozwiązania są coraz bardziej dostosowane do wysokowydajnych, czas rzeczywistych wykrywania ultra-niskich poziomów zanieczyszczeń i latentnych defektów, przy czym analityka oparta na AI ma stać się standardem w ciągu najbliższych kilku lat.

Patrząc w przyszłość, rynki wschodzące w Azji Południowej, Indii oraz na Bliskim Wschodzie będą rozwijały swoje własne zaawansowane ekosystemy produkcyjne. W miarę jak te regiony zwiększają zdolność, popyt na ultrapure testowanie redundancji nasili się, napędzając globalną współpracę i przyjęcie najlepszych technologii, aby zapewnić spójną jakość i wydajność w obliczu rosnącej złożoności chipów.

Perspektywy strategiczne: technologie zakłócające i długoterminowe trendy

Testowanie redundancji ultrapure w półprzewodnikach znajduje się na czołowej pozycji w zapewnianiu niezawodności, gdy geometrie urządzeń wciąż maleją, a złożoność fabryk rośnie. Do 2025 roku perspektywy strategiczne dla tej dziedziny są silnie kształtowane przez konwergencję technologii zakłócających oraz branżowe zmiany w kierunku produkcji zerowej wady, napędzane przez wymagania na AI, motoryzację oraz zaawansowane aplikacje logiczne.

Wiodący producenci półprzewodników szybko rozwijają swoje metody testowania redundancji, aby spełnić wyższe standardy czystości i wydajności. Na przykład TSMC podkreśla swoje zaangażowanie w zaawansowane wzmocnienie wydajności oraz rygorystyczne wykrywanie defektów w swoich najnowszych technologiach procesowych, integrując testowanie redundancji w liniach produkcyjnych ze wspomagającą AI analityką. Podobnie Intel inwestuje w systemy walidacji redundancji w czasie rzeczywistym, wykorzystując uczenie maszynowe do prognozowania i izolowania latentnych usterek w procesach produkcji węzłów 18A i 20A.

W 2025 roku kolejny istotny trend to przyjęcie zaawansowanych narzędzi metrologicznych i inspekcyjnych, zdolnych do wykrywania defektów na poziomie atomowym w ultrapure środowiskach. Applied Materials i Lam Research, wśród wiodących dostawców sprzętu półprzewodnikowego, wdrażają platformy inspekcyjne łączące obrazowanie e-beam, głębokie uczenie oraz procesy robocze uwzględniające redundancję, aby zapewnić szybkie zatrzymanie i korekcję odchyleń procesów. Te systemy mogą wykrywać i charakteryzować zanieczyszczenia na poziomie sub-nanometrów oraz usterki elektryczne, które są kluczowe w weryfikacji redundancji dla pamięci i układów logicznych.

Inny zakłócający trend to integracja testowania redundancji w inteligentnych platformach produkcyjnych. Samsung Semiconductor testuje obecnie monitorowanie redundancji napędzane przez AI, zintegrowane z cyfrowymi bliźniakami swoich fabryk, co pozwala na przewidywanie konserwacji oraz natychmiastowe przestrojenie procesów. To zmniejsza przestoje i zwiększa niezawodność produkcji najnowocześniejszych węzłów, bezpośrednio odpowiadając na oczekiwania zerowej wady w sektorach motoryzacyjnym i centrów danych.

Patrząc w przyszłość, perspektywy strategiczne dla testowania redundancji ultrapure w półprzewodnikach obejmują dalszą automatyzację i analitykę danych w chmurze. Konsorcja branżowe, takie jak SEMI, ustalają nowe standardy interoperacyjności protokołów testów oraz wymiany danych w całym łańcuchu dostaw, dążąc do uproszczenia weryfikacji redundancji na poziomie wafli i systemów. W miarę jak fabryki zwiększają uzależnienie od zaawansowanego testowania redundancji, spodziewaj się dalszej współpracy między producentami sprzętu, producentami chipów oraz dostawcami materiałów, aby przyspieszyć eliminację defektów w zamkniętej pętli i przesunąć granice niezawodności urządzeń do 2025 roku i później.

Źródła i odniesienia

- imec

- Advantest Corporation

- STMicroelectronics

- Synopsys

- ASML

- Infineon Technologies

- BASF

- DuPont

- Tokyo Electron Limited

- Samsung Electronics

- Entegris

- IEEE