Tabella dei Contenuti

- Sommario Esecutivo: 2025 e il Futuro

- Dimensione del Mercato e Previsioni di Crescita fino al 2030

- Principali Fattori Trainanti: AI, IoT e Manifattura Avanzata

- Standard Ultrapuri: Requisiti in Evoluzione e Benchmark Industriali

- Ultime Innovazioni nelle Metodologie di Test di Ridondanza

- Principali Attori e Alleanze Strategiche (Focus 2025)

- Integrazione della Supply Chain e Sfide di Purezza

- Ambiente Regolatorio e Organismi di Normativa (es. SEMI.org, IEEE.org)

- Mercati Emergenti e Opportunità Regionali

- Prospettiva Strategica: Tecnologie dirompenti e Tendenze a Lungo Termine

- Fonti e Riferimenti

Sommario Esecutivo: 2025 e il Futuro

Il test di ridondanza dei semiconduttori ultrapuri sta guadagnando un momento critico mentre l’industria entra nel 2025, spinta dall’incessante richiesta di nodi più piccoli, maggiore affidabilità dei dispositivi e dalla proliferazione di applicazioni avanzate come AI, elettronica automobilistica e calcolo quantistico. Ambienti ultrapuri sono essenziali per raggiungere i rigorosi requisiti di rendimento e affidabilità della fabbricazione di chip di sub-5nm e di prossima generazione. Il test di ridondanza—dove circuiti di backup e architetture a tolleranza ai guasti sono sistematicamente verificati—è diventato un perno per garantire la resilienza della produzione, minimizzare i costi di inattività e affrontare i difetti latenti che possono derivare da impurità o variazioni di processo anche minime.

I principali produttori di semiconduttori stanno aumentando gli investimenti nel test di ridondanza all’interno di ambienti ultrapuri. Ad esempio, la Taiwan Semiconductor Manufacturing Company (TSMC) continua ad ampliare il suo focus sulla convalida della ridondanza come parte delle sue strategie di controllo dei processi avanzati e gestione dei difetti, in particolare nei suoi nodi a 3nm e 2nm. Allo stesso modo, Samsung Electronics Semiconductor ha evidenziato l’integrazione di meccanismi di ridondanza e protocolli di test sofisticati nei suoi stabilimenti all’avanguardia, con l’obiettivo di rafforzare ulteriormente l’affidabilità dei dispositivi mentre si riduce a architetture transistor gate-all-around (GAA).

Anche i fornitori di attrezzature si stanno adattando a queste esigenze. Applied Materials e Lam Research stanno innovando strumenti di ispezione dei wafer e metrologia che sfruttano analisi guidate da AI per rilevare e caratterizzare i guasti di ridondanza in modo più efficiente nelle linee di processo ultrapure. Questi sistemi vengono implementati per monitorare la difettosità indotta dal processo e validare l’integrità operativa delle strutture ridondanti.

I dati dei consorzi industriali, come SEMI, indicano che gli investimenti in test e metrologia per schemi di ridondanza avanzati cresceranno a un CAGR superiore al 7% fino al 2028, riflettendo la priorità che il settore dà alla gestione del rendimento e alla garanzia di affidabilità. Inoltre, gli sforzi collaborativi come quelli presso imec stanno accelerando lo sviluppo di nuove architetture di ridondanza e protocolli di produzione su misura per ambienti ultrapuri.

Guardando al futuro, i prossimi anni vedranno il test di ridondanza diventare sempre più automatizzato, centrato sui dati e strettamente integrato con il controllo dei processi in tempo reale. Man mano che i produttori di semiconduttori si avvicinano ai 2nm e oltre, il paradigma zero difetti dipenderà dai progressi sia nel design della ridondanza sia nel testing all’interno di ambienti ultrapuri. Questa evoluzione sarà cruciale per sostenere l’affidabilità, la scalabilità e la fattibilità commerciale delle future tecnologie semiconduttori.

Dimensione del Mercato e Previsioni di Crescita fino al 2030

Il mercato globale per il test di ridondanza nei semiconduttori ultrapuri è pronto per una crescita significativa fino al 2030, trainato dall’aumento della complessità dei dispositivi semiconduttori, dalla proliferazione di nodi avanzati (5nm, 3nm e inferiori), e dalla crescente domanda di chip ultra-affidabili in applicazioni critiche come automobilistica, data center e AI. Con il ridimensionamento delle geometrie dei dispositivi e l’aumento dei livelli di integrazione, la necessità di garantire una purezza e robustezza assolute nei processi di fabbricazione dei semiconduttori ha posto il test di ridondanza al centro della garanzia di qualità.

Nel 2025, i principali produttori di semiconduttori come la Taiwan Semiconductor Manufacturing Company (TSMC), Samsung Electronics e Intel Corporation continuano ad espandere i loro investimenti in infrastrutture di test di ridondanza avanzata. Questi investimenti non sono solo mirati a rilevare e mitigare difetti latenti nei circuiti logici e di memoria, ma anche a soddisfare i requisiti di affidabilità sempre più rigorosi richiesti da settori automobilistici e critici. Ad esempio, le continue espansioni della capacità di TSMC e il loro focus sulle iniziative “Zero Defect” enfatizzano la centralità degli ambienti di test ultrapuri nel loro percorso.

Parallelamente agli investimenti nelle fonderie, i principali fornitori di attrezzature di test come Advantest Corporation e Teradyne, Inc. stanno rapidamente innovando per offrire soluzioni di attrezzature di test automatiche (ATE) di nuova generazione in grado di supportare il test di ridondanza a nodi di processo su nanometri. Questi sistemi sfruttano sempre più analisi guidate da AI e test paralleli ad alta capacità per migliorare la copertura e ridurre i tassi di fuga dei test, rispondendo alle esigenze in evoluzione delle fab moderne.

Secondo recenti comunicazioni aziendali e roadmaps del settore, il mercato per l’attrezzatura e i servizi di test di ridondanza nei semiconduttori ultrapuri è previsto crescere a un tasso di crescita annuo composto (CAGR) nell’area degli alti singoli cifre fino al 2030, con la regione Asia-Pacifico—dominata da Taiwan, Corea del Sud e Cina—che rimane il principale motore della domanda. L’espansione di nuove strutture di fabbricazione (“mega fab”) da parte di Samsung Electronics e TSMC nel 2025–2027 sottolinea ulteriormente la robusta prospettiva del settore.

Guardando al futuro, l’adozione della litografia ultravioletta estrema (EUV), dell’integrazione eterogenea e delle architetture chiplet guiderà una maggiore dipendenza dalle metodologie di test di ridondanza ultrapura. Gli sforzi collaborativi tra produttori, fornitori di attrezzature e consorzi industriali come SEMI sono attesi per accelerare lo sviluppo di standard e best practices, garantendo che i test di ridondanza seguano il ritmo della scalabilità tecnologica e delle esigenze di affidabilità fino al 2030 e oltre.

Principali Fattori Trainanti: AI, IoT e Manifattura Avanzata

L’evoluzione rapida dell’intelligenza artificiale (AI), dell’Internet delle cose (IoT) e della manifattura avanzata sta accelerando significativamente la domanda di test di ridondanza nei semiconduttori ultrapuri. Con l’aumento della complessità dei dispositivi e della densità di integrazione, soprattutto a nodi inferiori a 5 nm, garantire tolleranza ai guasti e operazioni affidabili diventa fondamentale. Gli acceleratori AI, ad esempio, ora richiedono test di ridondanza robusti per raggiungere i bassi tassi di difetti necessari per applicazioni critiche nei settori automobilistico, medico e industriale. Sia Intel Corporation che la Taiwan Semiconductor Manufacturing Company segnalano entrambi un crescente focus su schemi di ridondanza avanzati e protocolli di test per i loro ultimi nodi di processo, riflettendo un cambiamento dell’industria verso una maggiore affidabilità.

La proliferazione dell’IoT amplifica ulteriormente le esigenze di test di ridondanza. Con miliardi di sensori e dispositivi interconnessi previsti entro il 2025, i produttori devono garantire continuità operativa e sicurezza, anche in presenza di guasti hardware parziali. STMicroelectronics evidenzia che i suoi semiconduttori progettati per l’IoT subiscono estesi screening di ridondanza e affidabilità, sfruttando attrezzature di test automatiche capaci di simulare modalità di guasto complesse.

L’introduzione di architetture chiplet e packaging 3D a nodi avanzati sta anche trasformando le metodologie di test. I complessi sistemi multi-die richiedono non solo test funzionali tradizionali, ma anche verifiche di ridondanza a livello di sistema attraverso die interconnessi. Advanced Micro Devices (AMD) ha adottato nuove strategie di design-for-test (DFT) consapevoli della ridondanza per i suoi processori basati su chiplet, mentre Synopsys e Advantest stanno implementando soluzioni di test di nuova generazione per affrontare i requisiti unici di tolleranza ai guasti di queste architetture.

- Dati e Tendenze (2025 e Oltre): Le aziende fabless e le fonderie stanno aumentando la loro copertura di test e i budget di screening della ridondanza, con una crescita riportata del 18% anno su anno nella spesa per attrezzature di test avanzate (ASML). I punti di inserimento per test di wafer e pacchetti finali si stanno espandendo, soprattutto per i chip destinati ad applicazioni AI e IoT critiche per la sicurezza.

- Prospettive: Nei prossimi anni, ci si aspetta che i produttori di semiconduttori abbraccino ulteriormente la generazione di modelli di test basati su AI e strategie di ridondanza adattativa, riducendo le fughe dai test e migliorando l’affidabilità sul campo. L’integrazione del monitoraggio della ridondanza in tempo reale nei dispositivi distribuiti—abilitato dall’AI edge e dai gemelli digitali—spingerà i limiti della rilevazione e correzione dei guasti in campo (Infineon Technologies).

In sintesi, la convergenza di AI, IoT e manifattura avanzata sta costringendo l’industria a ridefinire i paradigmi dei test di ridondanza nei semiconduttori ultrapuri, con significativi investimenti e innovazioni previsti fino al 2025 e oltre.

Standard Ultrapuri: Requisiti in Evoluzione e Benchmark Industriali

Il test di ridondanza ultrapura sta diventando una pietra miliare della produzione di semiconduttori poiché le geometrie dei dispositivi continuano a rimpicciolirsi e la complessità funzionale aumenta. La necessità di garantire un fornitura ininterrotta di acqua ultrapura (UPW), sostanze chimiche e gas ha spinto nuovi standard e benchmark per i test di ridondanza in tutto il settore. Nel 2025, il settore sta assistendo a una convergenza di controllo dei processi rigorosi, automazione e analisi dei dati per mantenere questi requisiti esigenti.

I principali produttori stanno implementando ridondanza multilivello nei loro sistemi ultrapuri per mitigare qualsiasi rischio di contaminazione o inattività. Ad esempio, Intel riporta che le sue fabbriche di wafer ora utilizzano loop UPW dual-feed, treni di filtrazione paralleli e sensori in tempo reale per passare automaticamente a sistemi di backup se viene rilevata una deviazione. Questa ridondanza viene continuamente testata attraverso simulazioni e prove pratiche, garantendo che tutti i nodi critici possano mantenere una purezza di grado semiconduttore (<18 MΩ·cm per UPW) anche in scenari avversi.

Sul lato della fornitura chimica, aziende come BASF e DuPont stanno collaborando con i produttori di dispositivi per convalidare infrastrutture di consegna e stoccaggio ridondanti. Questi sistemi sono sottoposti a test di sfida periodici, dove l’approvvigionamento primario viene interrotto intenzionalmente e il passaggio automatico a backup viene monitorato sia per velocità sia per garanzia di purezza. I dati da questi test vengono condivisi con i clienti, formando parte delle verifiche di qualità dei fornitori e della conformità agli standard del settore come SEMI F63 e linee guida ITRS (SEMI).

Le prospettive per i prossimi anni indicano un ulteriore inasprimento dei benchmark. L’organizzazione SEMI sta attivamente revisionando i suoi standard per la convalida della ridondanza, enfatizzando la tracciabilità digitale, la registrazione degli eventi e l’analisi predittiva dei guasti. I fornitori di attrezzature come Evoqua Water Technologies stanno ora offrendo pacchetti di test integrati, combinando test fisici di passaggio con diagnosi basate su cloud per fornire verifica continua.

La spinta verso tecnologie di processo sub-2 nm è destinata a guidare protocolli di test di ridondanza ancora più rigorosi. La condivisione di dati in tempo reale tra produttori e fornitori, come dimostrato dalle recenti iniziative di TSMC, sta diventando una prassi standard. Questo approccio collaborativo non solo aumenta la resilienza, ma garantisce anche una risposta rapida alle anomalie, stabilendo nuovi benchmark industriali per affidabilità e integrità del processo in un ambiente in cui ogni lapse può avere ramificazioni multimilionarie.

Ultime Innovazioni nelle Metodologie di Test di Ridondanza

La produzione di semiconduttori ultrapuri continua a spingere i limiti delle prestazioni dei dispositivi, con metodologie di test di ridondanza che evolvono rapidamente per garantire affidabilità in circuiti integrati (IC) sempre più complessi. Con il diminuzione delle geometrie dei dispositivi e l’aumento della richiesta di rendimenti ultra-alti, il test di ridondanza—particolarmente per array di memoria e logica—è diventato un punto focale di innovazione.

Nel 2025, i principali produttori di semiconduttori stanno implementando soluzioni avanzate di analisi e riparazione della ridondanza integrate nei loro flussi di test. Ad esempio, la Taiwan Semiconductor Manufacturing Company (TSMC) ha evidenziato l’uso di algoritmi di ridondanza adattivi nei suoi nodi di processo a 3nm e 2nm, sfruttando i dati dei test in linea e l’apprendimento automatico per la localizzazione dinamica dei difetti e l’allocazione di celle di riserva. Questo approccio riduce l’eccesso e il difetto, migliorando sia il rendimento che l’affidabilità a lungo termine.

Nei prodotti di memoria, Samsung Electronics ha implementato valutazioni di ridondanza in tempo reale nelle sue ultime linee di DRAM e NAND flash. Circuiti avanzati di autori riparazione incorporata (BISR), supportati da analisi predittive, consentono l’identificazione rapida e la sostituzione di celle difettose durante la selezione del wafer, anche quando le dimensioni degli array superano le centinaia di gigabit. Queste innovazioni minimizzano il rischio di guasti latenti dopo l’implementazione e ottimizzano l’utilizzo degli elementi ridondanti on-chip.

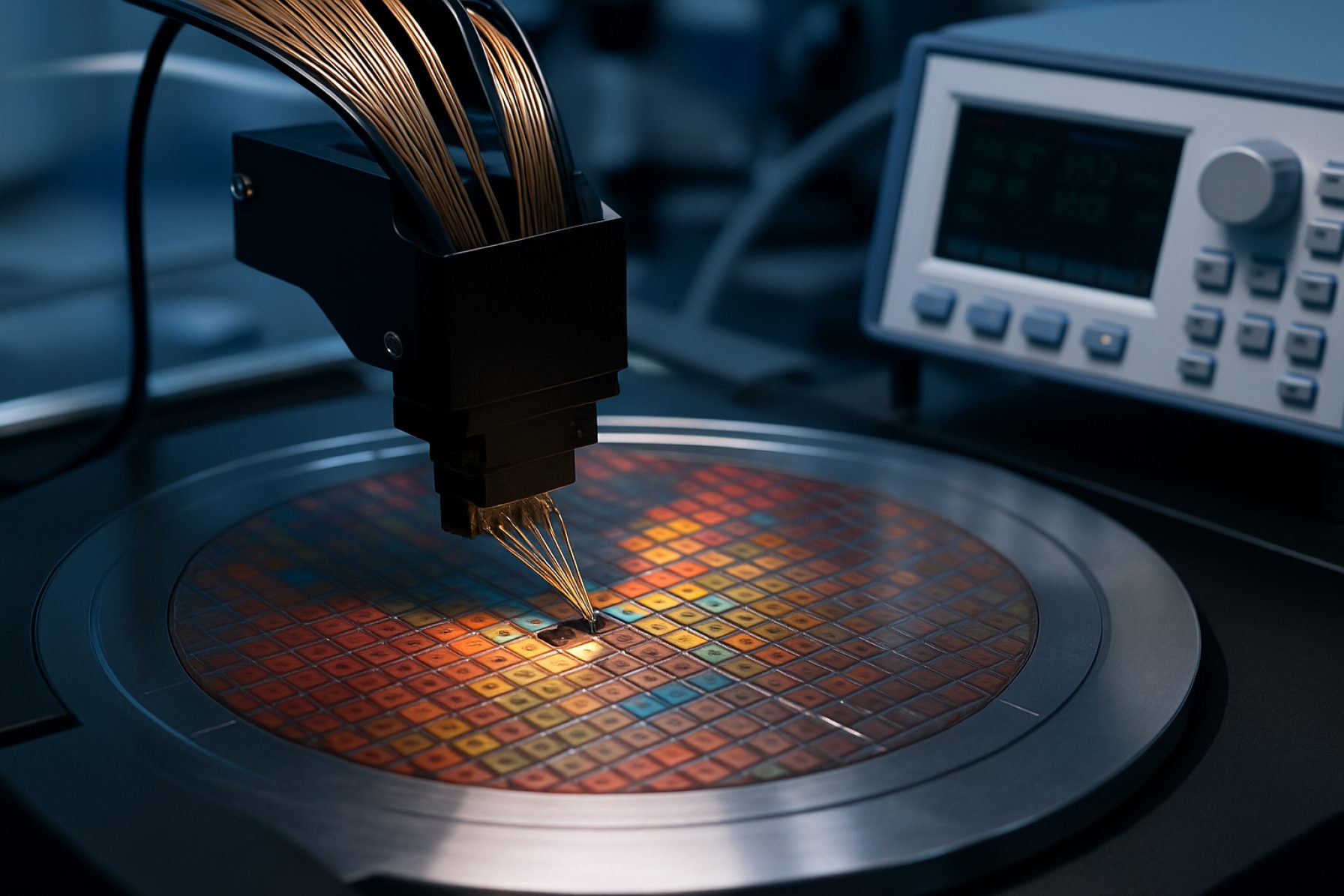

I fornitori di attrezzature di test (ATE) come Advantest Corporation stanno introducendo nuove piattaforme con supporto nativo per protocolli di test consapevoli della ridondanza. La loro serie V93000, lanciata nel 2024, consente test paralleli e riparazioni in situ per pacchetti multi-die e chiplet—una caratteristica chiave man mano che il packaging avanzato si diffonde nell’informatica ad alte prestazioni e nelle applicazioni di intelligenza artificiale.

L’ecosistema delle attrezzature per semiconduttori sta anche rispondendo alla necessità di ambienti di test ultraclean. Lam Research ha riportato progressi nella manipolazione dei wafer senza contaminanti e nelle camere di processo nel 2025, supportando direttamente l’integrità del test di ridondanza per nodi all’avanguardia in cui anche le impurità a livello atomico possono distorcere i dati di rendimento o mascherare difetti di ridondanza latenti.

Guardando al futuro, si prevede che una convergenza di analisi dei dati, ottimizzazione co-progettazione hardware-software e un controllo di processo più rigoroso migliori ulteriormente il test di ridondanza. L’integrazione di gemelli digitali e predizione dei difetti guidata dall’AI è all’orizzonte, promettendo una produzione quasi senza difetti mentre la complessità dei dispositivi cresce. La collaborazione tra fonderie, produttori di attrezzature e progettisti fabless sarà essenziale per realizzare questi progressi e mantenere la fornitura di semiconduttori ultrapuri e ultra-affidabili.

Principali Attori e Alleanze Strategiche (Focus 2025)

Nel 2025, il panorama dei test di ridondanza dei semiconduttori ultrapuri è caratterizzato da una significativa attività tra i principali attori del settore, alleanze strategiche e investimenti in soluzioni di testing avanzate. Con la continua riduzione dei nodi di produzione dei semiconduttori, la domanda di ambienti ultrapuri e test di ridondanza robusti è aumentata notevolmente. I principali attori—compresi i produttori di attrezzature, le fonderie di semiconduttori e i fornitori di materiali—stanno collaborando sempre più per affrontare i rigorosi requisiti di rilevamento dei difetti e affidabilità dei processi.

- Applied Materials, Inc. rimane all’avanguardia, fornendo piattaforme avanzate di ispezione e metrologia che consentono test di ridondanza a scale nanometriche. Nel 2025, l’azienda ha annunciato espansioni nella sua collaborazione con i principali produttori di logica e memoria per co-sviluppare moduli di ispezione per la ridondanza di nuova generazione ottimizzati per ambienti ultrapuri (Applied Materials, Inc.).

- ASML Holding NV continua a svolgere un ruolo fondamentale, in particolare attraverso i suoi sistemi di litografia EUV, che richiedono rigorosi test di ridondanza in linea per garantire la stabilità operativa. All’inizio del 2025, ASML ha ampliato la sua alleanza con i principali produttori di chip per integrare procedure di test di ridondanza proprietarie all’interno degli strumenti EUV, mirando a minimizzare la contaminazione e il tempo di inattività non pianificato (ASML Holding NV).

- Tokyo Electron Limited (TEL) ha approfondito le sue partnership con fonderie globali e aziende fabless, concentrandosi sulla co-innovazione per moduli di processo ultrapuri e verifica della ridondanza. Le iniziative del 2025 di TEL includono programmi pilota con importanti fab in Asia per perfezionare algoritmi di test automatici per la gestione del rendimento critico (Tokyo Electron Limited).

- Samsung Electronics e TSMC—i più grandi produttori di semiconduttori al mondo—hanno entrambi investito in innovazioni interne nei test di ridondanza. Nel 2025, Samsung ha annunciato l’implementazione di una piattaforma di monitoraggio della ridondanza guidata da AI su tutte le sue linee logiche avanzate, mentre TSMC ha ampliato il suo programma di qualificazione della ridondanza multi-fornitore per includere nuovi protocolli di test per i nodi di processo a 2 nm (Samsung Electronics; TSMC).

- Alleanze industriali, come quelle coordinate da SEMI, hanno ulteriormente accelerato l’armonizzazione degli standard di test e delle best practices, con nuovi gruppi di lavoro nel 2025 focalizzandosi specificamente sulla verifica della ridondanza negli ambienti di produzione ultrapuri (SEMI).

Guardando avanti, il settore è previsto vedere una continua convergenza tra fornitori di attrezzature e produttori di dispositivi, con alleanze strategiche sempre più centrate sulla co-sviluppo di soluzioni di test di ridondanza personalizzate e in linea. Questo approccio collaborativo è destinato a sostenere la prossima ondata di innovazione nella produzione di semiconduttori ultrapuri, garantendo sia rese più elevate sia maggiore affidabilità dei dispositivi fino al 2026 e oltre.

Integrazione della Supply Chain e Sfide di Purezza

Il test di ridondanza nei semiconduttori ultrapuri sta diventando un aspetto fondamentale dell’integrazione della supply chain mentre l’industria dei semiconduttori affronta requisiti di purezza sempre più severi e una crescente complessità nei processi di produzione. Con il ridimensionamento delle geometrie dei chip e la sensibilità dei dispositivi ai contaminanti che aumenta, garantire l’affidabilità e la purezza sia dei materiali che dei prodotti finiti attraverso il test di ridondanza è emersa come una sfida sia tecnica che logistica.

Nel 2025, l’attenzione è rivolta all’integrazione di protocolli avanzati di test di ridondanza attraverso la supply chain. Grandi fonderie e fornitori di materiali stanno ora richiedendo test a più fasi di gas ultrapuri, sostanze chimiche e wafer di silicio a diversi nodi di lavorazione per minimizzare il rischio di introduzione di difetti legati a contaminanti non rilevati. Ad esempio, Intel Corporation ha delineato strategie per test inline e di fine processo ridondanti delle sostanze chimiche di processo per garantire che guasti o contaminazione in qualsiasi punto siano rapidamente rilevati e isolati prima di influenzare i rendimenti di produzione.

Un altro sviluppo chiave è l’iniziativa collaborativa per metriche di purezza e metodologie di test standardizzate da parte di organismi di settore come SEMI. Nel 2024 e nel 2025, il programma di standardizzazione internazionale di SEMI sta lavorando con i produttori di chip, i fornitori di attrezzature e i venditori di sostanze chimiche per perfezionare i protocolli per la convalida della purezza ridondante, inclusa la verifica a doppia sorgente dei lotti chimici e il monitoraggio in tempo reale dei flussi di gas. Tali iniziative affrontano direttamente l’integrazione della supply chain stabilendo aspettative uniformi e requisiti di condivisione dei dati tra fornitori e produttori.

I principali fornitori di materiali come Entegris e DuPont stanno investendo in reti di sensori avanzate e analisi automatizzate per consentire controlli di purezza continui e ridondanti. Questi sistemi possono rintracciare i contaminanti fino a livelli di parti per trilione, fornendo dati azionabili che vengono condivisi con partner a valle come parte di un quadro di assicurazione qualità integrato. Questo è particolarmente cruciale mentre l’industria guarda ai nodi di processo sub-2nm, dove anche le impurità traccia possono compromettere l’integrità del dispositivo.

Guardando avanti, nei prossimi anni si prevede che il test di ridondanza diventi non solo più automatizzato ma anche più profondamente integrato nei sistemi di gestione della supply chain digitale. Le aziende stanno sviluppando soluzioni di tracciabilità basate su blockchain e piattaforme di condivisione dati sicure per registrare e verificare ogni risultato di test di purezza lungo la supply chain, come dimostrato da TSMC e i suoi partner ecosistemici. Questa digitalizzazione aiuterà a identificare possibili rotture o lapse nella ridondanza prima che possano influenzare la produzione ad alto volume, proteggendo ulteriormente la purezza e l’affidabilità dei semiconduttori avanzati.

Ambiente Regolatorio e Organismi di Normativa (es. SEMI.org, IEEE.org)

Il panorama regolatorio per il test di ridondanza nei semiconduttori ultrapuri è in rapida evoluzione mentre l’industria affronta sia progressi tecnologici che crescenti domande di affidabilità dei dispositivi. Ambienti ultrapuri sono critici per la fabbricazione dei semiconduttori, con anche una minima contaminazione a rischio di guasto del wafer o difetti latenti del dispositivo. Il test di ridondanza—implementando molteplici metodologie di test o sistemi di backup—è diventato un’area di focus per garantire che i processi di test stessi siano abbastanza robusti da rilevare e mitigare possibili guasti.

Organizzazioni chiave di sviluppo standard come SEMI e IEEE stanno svolgendo ruoli chiave nella definizione dell’ambiente regolatorio per il test di ridondanza. Ad esempio, lo standard SEMI F63 affronta linee guida per la qualità dell’acqua ultrapura (UPW) nella fabbricazione di semiconduttori, influenzando indirettamente i protocolli di ridondanza specificando limiti di rischio di contaminazione e requisiti di monitoraggio. Nel 2025, SEMI continua ad aggiornare gli standard relativi al test e al monitoraggio di sistemi UPW e gas, che sono integrali alle strategie di ridondanza in passi di processo critici.

Allo stesso modo, l’IEEE ha iniziative in corso all’interno della sua Associazione di Standardizzazione rilevanti per la ripetibilità dei metodi di test, tolleranza ai guasti del sistema e ridondanza nella qualifica dei dispositivi semiconduttori. IEEE 1687 (IJTAG) e standard correlati contribuiscono a creare quadri per l’accesso a strumenti incorporati per la rilevazione della ridondanza e monitoraggio dei guasti in tempo reale. Man mano che i dispositivi diventano più complessi e i nodi di processo si riducono, gli standard di test enfatizzano sempre più la ridondanza non solo nelle routine di test ma anche nelle architetture di test automatico integrato (BIST) on-chip.

Negli ultimi anni, enti regolatori globali e consorzi industriali hanno enfatizzato l’armonizzazione delle best practices. Il programma di standardizzazione internazionale di SEMI, ad esempio, facilita l’allineamento transfrontaliero sui requisiti di monitoraggio e verifica della ridondanza, riflettendo la natura globalizzata delle supply chain di semiconduttori. Nel 2025, i comitati tecnici di SEMI stanno dando priorità alla collaborazione con le autorità regionali per garantire che i protocolli di test di ridondanza soddisfino i requisiti normativi locali e gli standard internazionali.

Guardando ai prossimi anni, si prevede che l’ambiente regolatorio diventi ulteriormente rigoroso. Con la proliferazione di applicazioni ad alta affidabilità—come automobilistica, aerospaziale e elettroniche sanitarie—le autorità potrebbero richiedere test di ridondanza e documentazione più rigorosi. Organismi di standardizzazione come SEMI e IEEE sono previsti rilasciare nuove linee guida che affrontano metodi avanzati di verifica della ridondanza, con requisiti crescenti per tracciabilità digitale, analitiche predittive e supervisione dei test guidata dall’AI. Gli stakeholder di tutto il settore dovranno rimanere agili, adattando proattivamente questi standard in evoluzione per mantenere la conformità e il vantaggio competitivo.

Mercati Emergenti e Opportunità Regionali

Il panorama per il test di ridondanza nei semiconduttori ultrapuri sta evolvendo rapidamente nel 2025, plasmato dall’espansione globale della produzione avanzata di chip e dall’aumento della complessità dei circuiti integrati. Con le principali fonderie che investono in nodi di prossima generazione—come 3nm e inferiori—la domanda di protocolli di test di ridondanza rigorosi in ambienti ultrapuri è in aumento, specialmente nei nuovi hub di produzione semiconduttori.

Nel 2025, si osserva una crescita significativa nella regione Asia-Pacifico, con Taiwan, Corea del Sud e Cina continentale a guidare gli investimenti in nuova capacità di fabbricazione. La Taiwan Semiconductor Manufacturing Company (TSMC) e Samsung Electronics stanno espandendo le loro capacità di processo avanzato con un forte focus sulla minimizzazione della contaminazione e sulla garanzia della ridondanza nei passi di processo critici. Queste aziende stanno integrando test di ridondanza avanzati per conformarsi a standard sempre più rigorosi in termini di difettosità e affidabilità, in particolare nei chip automobilistici e centrati sull’AI.

Nel frattempo, gli Stati Uniti stanno assistendo a un ripristino nella produzione di semiconduttori, sostenuto da incentivi federali e partnership con fornitori locali. Intel sta attivamente costruendo nuove fabbriche in Arizona e Ohio, con un’enfasi sul dispiegamento di sistemi di test di ridondanza per flussi di processo ultrapuri. Questi sistemi sfruttano ispezioni di difetti in linea e analisi in tempo reale per rilevare e mitigare potenziali punti di guasto, migliorando così il rendimento e l’affidabilità per applicazioni critiche.

In Europa, l’emergere di nuove strutture da parte di GlobalFoundries e la continua crescita di Infineon Technologies stanno alimentando la domanda di test di ridondanza all’avanguardia. La “Legge sui Chip” dell’Unione Europea mira a raddoppiare la produzione di chip della regione entro il 2030, stimolando investimenti in acqua ultrapura, gas e tecnologie di controllo della contaminazione che dipendono da robusti test di ridondanza per soddisfare severi requisiti di qualità.

Fornitori di tecnologie specializzati in test di ridondanza—come Advantest Corporation e Teradyne—riportano un aumento degli ordini sia da fab consolidati che da nuovi entranti in queste regioni. Le loro soluzioni sono sempre più progettate per la rilevazione in tempo reale di contaminanti e difetti latenti a elevatissima portata, con analisi guidate da AI previste per diventare standard nei prossimi anni.

Guardando avanti, i mercati emergenti nel sud-est asiatico, in India e in Medio Oriente si preparano a sviluppare i propri ecosistemi avanzati di produzione. Con l’aumento della capacità in queste regioni, la domanda di test di ridondanza ultrapuri intensificherà, guidando la collaborazione globale e l’adozione di tecnologie migliori per garantire qualità e rendimento costanti di fronte a un aumento della complessità dei chip.

Prospettiva Strategica: Tecnologie dirompenti e Tendenze a Lungo Termine

Il test di ridondanza nei semiconduttori ultrapuri è posizionato all’avanguardia per garantire affidabilità mentre le geometrie dei dispositivi continuano a rimpicciolirsi e le complessità delle fabbriche aumentano. Entro il 2025, la prospettiva strategica di questo campo è fortemente influenzata da una convergenza di tecnologie dirompenti e cambiamenti dell’industria verso una produzione zero difetti, guidata dalle richieste dell’AI, dell’automotive e delle applicazioni logiche avanzate.

I principali produttori di semiconduttori stanno rapidamente evolvendo le loro metodologie di test di ridondanza per soddisfare standard più elevati di purezza e rendimento. Ad esempio, TSMC ha evidenziato il suo impegno per il miglioramento del rendimento avanzato e il rilevamento rigoroso dei difetti nelle sue ultime tecnologie di processo, integrando test di ridondanza in linea e analisi alimentate da AI direttamente nelle sue linee di produzione. Allo stesso modo, Intel sta investendo in sistemi di convalida della ridondanza in tempo reale, sfruttando l’apprendimento automatico per prevedere e isolare guasti latenti nei loro flussi di produzione a nodo 18A e 20A.

Una tendenza significativa nel 2025 è l’adozione di strumenti avanzati di metrologia e ispezione capaci di rilevare difetti a scala atomica in ambienti ultrapuri. Applied Materials e Lam Research, tra i principali fornitori di attrezzature per semiconduttori al mondo, stanno distribuendo piattaforme di ispezione che combinano imaging a fascio elettronico, apprendimento profondo e flussi di lavoro consapevoli della ridondanza per garantire che le escursioni di processo possano essere contenute e corrette rapidamente. Questi sistemi possono rilevare e caratterizzare contaminazione sub-nanometrica e guasti elettrici, che sono fondamentali nella validazione della ridondanza per chip di memoria e logica.

Un altro trend dirompente è l’integrazione del test di ridondanza nelle piattaforme di smart manufacturing. Samsung Semiconductor sta sperimentando un monitoraggio della ridondanza guidato da AI integrato con gemelli digitali delle sue fabbriche, consentendo manutenzione predittiva e ricalibrazione istantanea dei processi. Questo riduce i tempi di inattività e aumenta l’affidabilità della produzione a nodo avanzato, affrontando direttamente le aspettative di zero difetti del mercato automobilistico e dei datacenter.

Guardando avanti, la prospettiva strategica per il test di ridondanza nei semiconduttori ultrapuri prevede ulteriore automazione e analisi dei dati basate su cloud. I consorzi industriali come SEMI stanno stabilendo nuovi standard per l’interoperabilità dei protocolli di test e la condivisione dei dati lungo la supply chain, mirano a semplificare la verifica della ridondanza dalla wafer al livello di sistema. Man mano che le fabbriche aumentano la loro dipendenza dai test di ridondanza avanzati, ci si aspetta ulteriori collaborazioni tra produttori di attrezzature, produttori di chip e fornitori di materiali per accelerare l’eliminazione dei difetti in ciclo chiuso e spingere i limiti dell’affidabilità dei dispositivi fino al 2025 e oltre.

Fonti e Riferimenti

- imec

- Advantest Corporation

- STMicroelectronics

- Synopsys

- ASML

- Infineon Technologies

- BASF

- DuPont

- Tokyo Electron Limited

- Samsung Electronics

- Entegris

- IEEE